Other Parts Discussed in Thread: ADS52J90

您好!

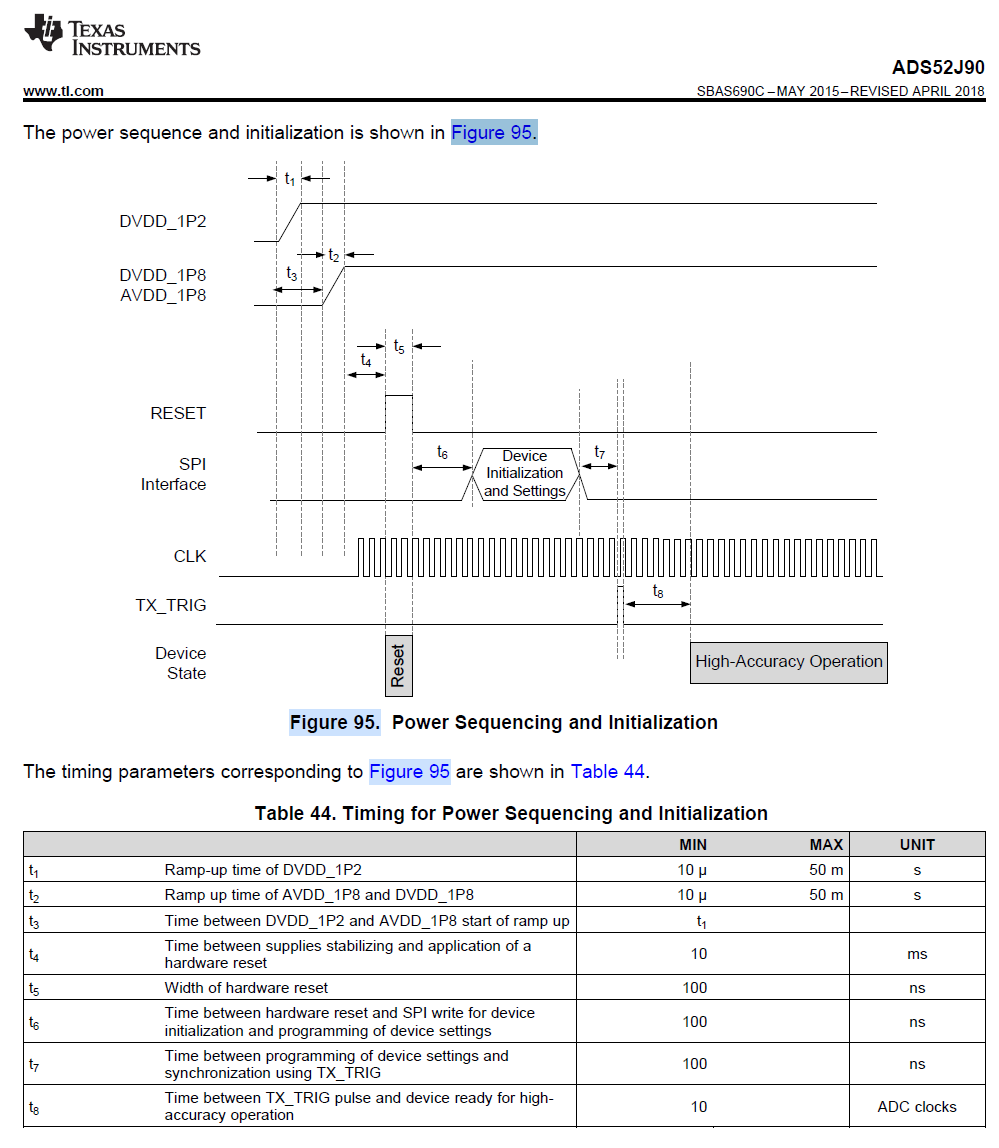

我们的设计使用两个 ADS52J90 ADC。 我们想重新访问下面这个数据表部分中指定的启动时序、并要求更新指导。

首先、我们确认我们遵守下面示波器捕获的 T1、T2、T3和 T4。 T4很容易实现、因为在这段时间间隔内、一个人必须对 FPGA 进行编程。

我们在另一个 E2E 论坛帖子中看到、TI 建议对 T5使用比数据表中建议的更长的期限。 我们还怀疑需要扩展 T6、t7和 T8的某些组合。 我们的证据包括 DCLKP 和 DCLKM 上的稳定时间较长(请参阅下图)。 数据表显示、我们可以在~300ns 内开始校准 LVDS 通道、外加对 SPI 进行编程的时间。 下面的屏幕截图显示了在额定条件下复位后、DCLK 仍然稳定在25us 至30us 之间。 这意味着比数据表中建议的时间更长的 T6+t7+T8时间。

超过这一点、我们的设计仍然不稳定。 您对此特定的启动观察结果有什么意见吗? 或者、更广泛地说、您是否有其他我们应该了解的与初始化相关的社区学习?

谢谢!

Tyler