您好!

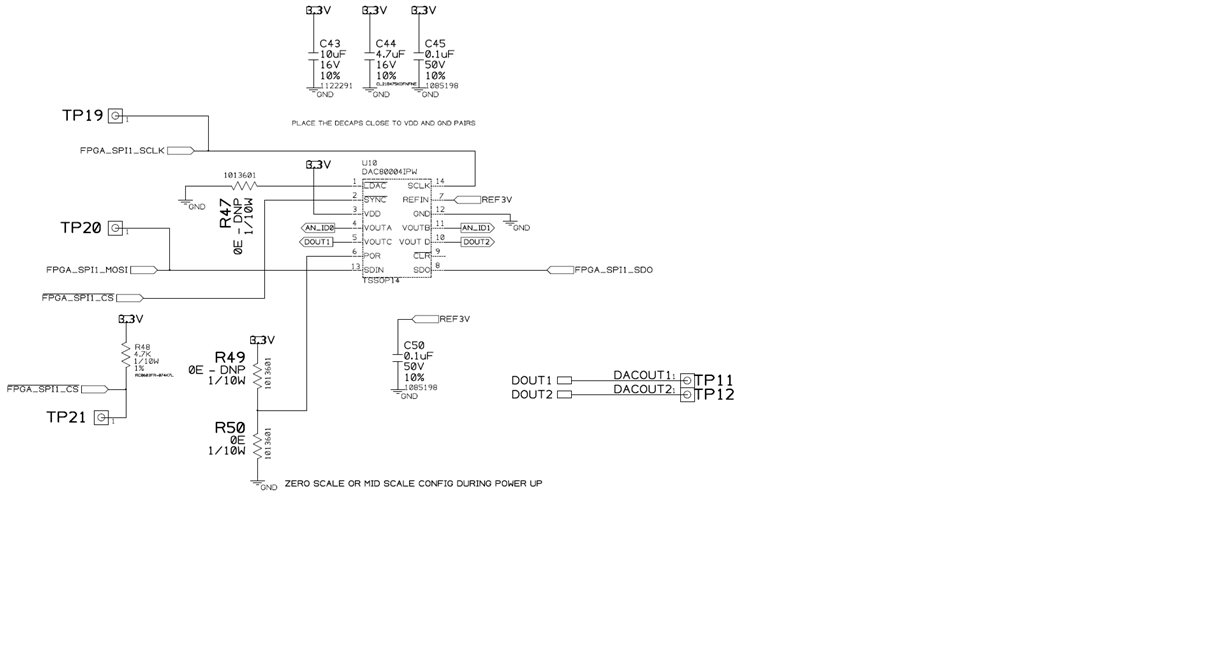

在我的 DAC80004IPW 设计中、CLR 引脚保持悬空。 我看不到 DAC 输出根据编程的 DAC 输入代码发生变化。

LDAC 引脚通过2K 电阻器接地、POR 接地(零标度)。 还提供了中量程(连接到 VDD)。 输出适用于零标度和中标度硬件配置。

我需要您的意见来解决这个问题。 我已附上原理图。 请发表评论。

谢谢

在

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

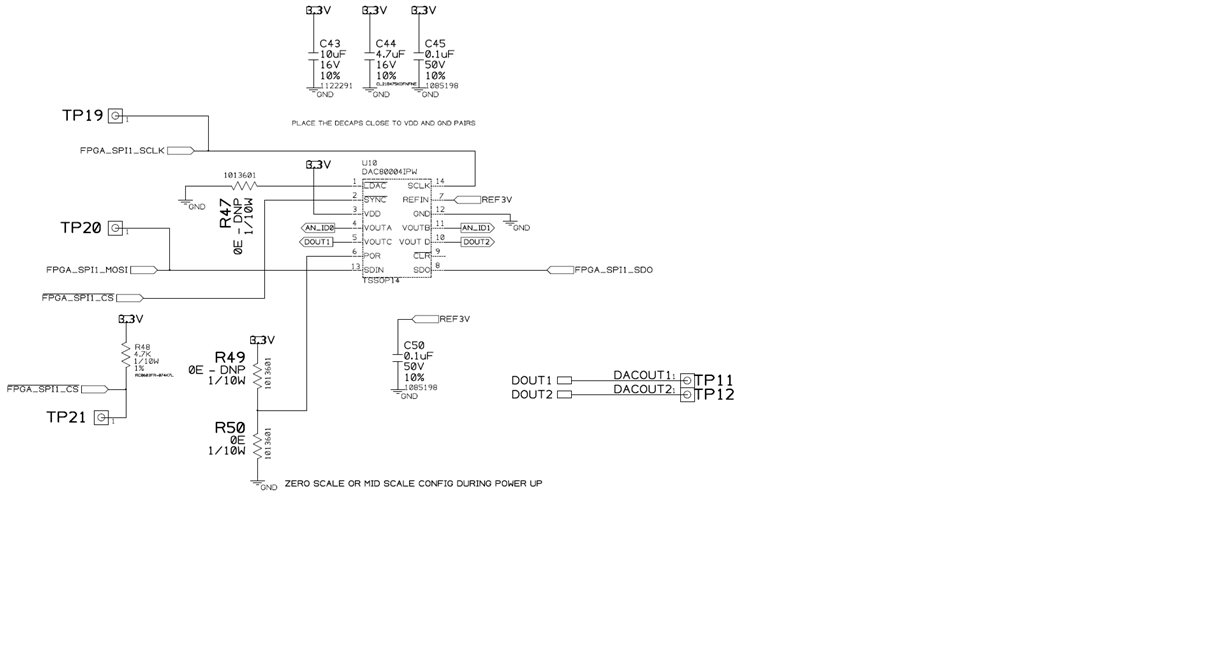

在我的 DAC80004IPW 设计中、CLR 引脚保持悬空。 我看不到 DAC 输出根据编程的 DAC 输入代码发生变化。

LDAC 引脚通过2K 电阻器接地、POR 接地(零标度)。 还提供了中量程(连接到 VDD)。 输出适用于零标度和中标度硬件配置。

我需要您的意见来解决这个问题。 我已附上原理图。 请发表评论。

谢谢

在

在、

不知为何我在原答覆中遗漏了对悬空 CLR 引脚的评论。 虽然从技术上讲、引脚对下降沿很敏感、但如果引脚未使用、则不建议将其保持悬空、并且一定要将其连接到 VDD、以检查您的器件是否意外被保持在清零状态。

您的 MCU 的时钟相位和极性设置是什么? 由于图的比例、我不能很好地确定时序、但看起来数据在 SDIN 上与下降时钟边沿同时发生变化。 数据会在 SCLK 的下降沿移入器件、因此存在一些锁存无效或意外数据的风险、因此您在输出端看不到所需的结果。 通常、对于下降沿关键接口、我希望看到数据在上升沿发生变化、以便满足设置和保持时序要求、因此您的解决方法可能与更改 CPOL 和 CPHA 设置一样简单。