请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC7551-Q1 。 我们对您的 DAC7551-Q1感兴趣。 我们希望使用 SPI 接口来访问它。 但我们对其串行写入操作时序有疑问。

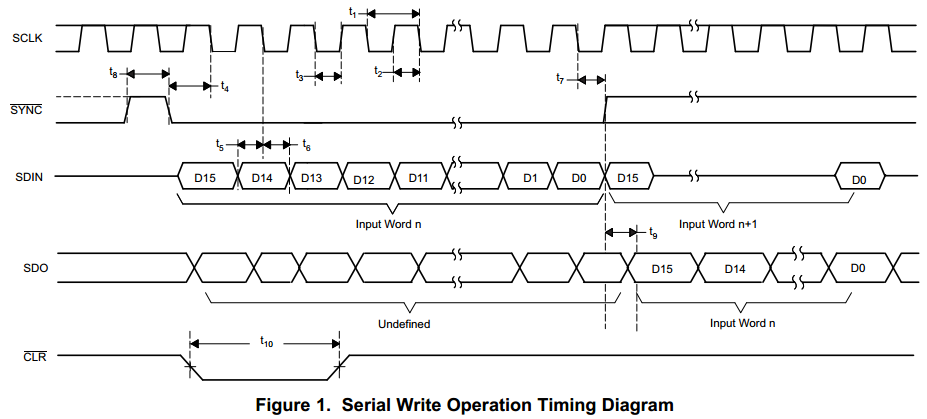

- 数据表指出、t7 (SCLK 下降沿到同步上升沿的时间)不应超过(t1–10ns)来锁存正确的数据。 此要求似乎不是 SPI 协议中的正常要求。 从我的角度来看、t7是一个保持时间、因此它应该具有最小值而不是最大值。 如果我们只向 DAC 写入16位数据一次、然后 SCLK 保持高电平、t7在这种情况下是否会超过(t1–10ns)?