主题中讨论的其他器件:LMK01000、 DAC3482

您好!

我从自己的板上运行 DAC3482。 Xilinx K7 FPGA 用于通过 LVDS 驱动 DAC 并控制板载 DDR 存储器。 一个外部1228.8MHz 时钟源被应用于 LMK01000、然后被分配给 DAC 和 FPGA。

DAC CLK = 1228.8MHz

内插= x4

16位数据模式

2的组件已禁用[数据范围0 ~ 65535 ]

如果频率= DAC CLK/16 = 76.805MHz、则为 DAC

MSP430 MCU 对 DAC 进行了如下配置:

DAC3482_RST_LOW;

delay_ms (10);

DAC3482_RST_HIGH;

DAC3482_TXEN_LOW;

unsigned int cfg2 = 0;

if (Dac3482_twos) cfg2|= BIT1;//2已禁用

//if (Dac3482_xIF) cfg2|= BIT4;

Dac3482WriteSpi (0x0280D0 | cfg2);

unsigned int cfg0 = Dac3482_XINT>>>1;//Dac3482_XINT = 4

cfg0 = cfg0 <<8;

cfg0 = cfg0 + 0x1C + BIT7;

Dac3482WriteSpi (cfg0);//Reg 00

Dac3482WriteSpi (0x01020E);//Reg 01

Dac3482WriteSpi (0x03A000);//Reg 03

Dac3482WriteSpi (0x103000);//Reg 10

Dac3482WriteSpi (0x140000);//Reg 14 - 15:0

unsigned long cfg15 = 0x150000;

if (Dac3482_xIF>1)

cfg15 = cfg15 + 0x10000/Dac3482_xIF;//Dac3482_xIF = 16

Dac3482WriteSpi (cfg15);//Reg 15 - 31:16

Dac3482WriteSpi (0x1B0800);//Reg 1B

Dac3482WriteSpi (0x1F8180);//Reg 1F

Dac3482WriteSpi (0x202201);//Reg 20

//帧

//FPGA RST

FPGA_RST_LOW;

delay_ms (100);//应用帧

Dac3482WriteSpi (0x050000);//Reg 5

Dac3482WriteSpi (0x1F818A);//Reg 1F

Dac3482WriteSpi (cfg0);//Reg 0

Dac3482WriteSpi (0x1F8188);//Reg 1F

Dac3482WriteSpi (0x200001);//Reg 20

delay_ms (100);

DAC3482_TXEN_HIGH;

这里是一些测试数据、

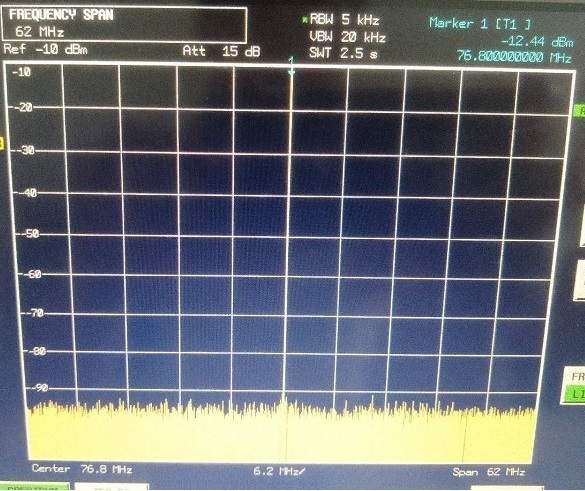

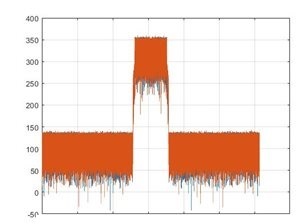

DAC IF 输出(无 IQ 数据)

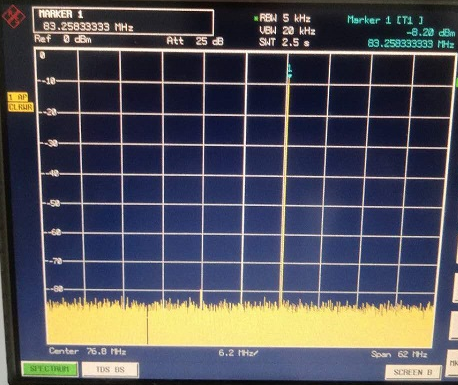

播放48点正弦波(数据文件包含819200个周期)

数据频率= DAC clk / 48 / 4 = 6.4MHz;输出频率= 76.805 + 6.4 = 83.205M

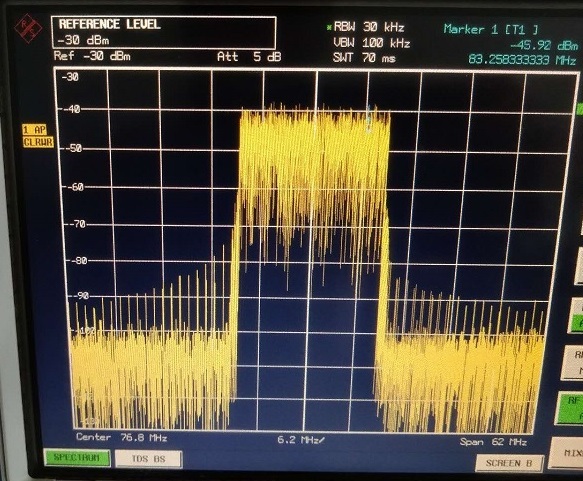

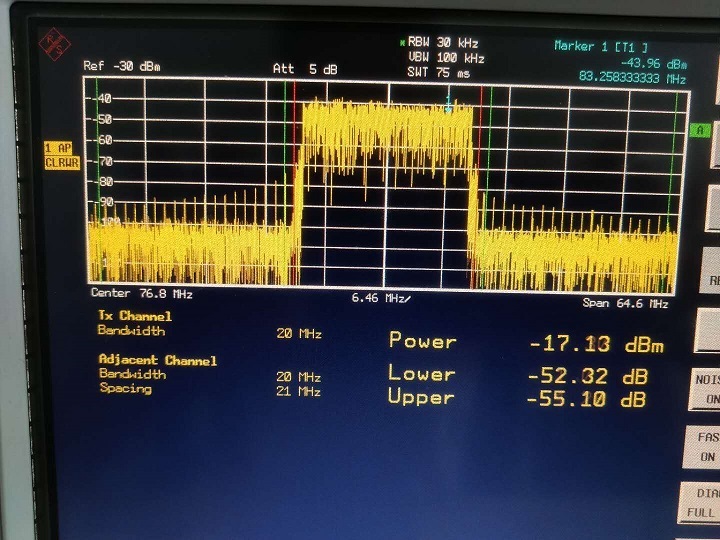

播放20M LTE 波形(307.2M 采样率)

在 Matlab 中、LTE 波形数据文件频谱是纯净的;该数据文件也由 HSDC+TSW1400+TSW3085进行验证。 因此、波形文件不能成为原因。

我不明白为什么在使用调制数据时会有如此刺激的刺激、而正弦波的一切都正常。

是否有人可以帮助消除这些杂散?

任何想法都将受到高度赞赏。

提前感谢!

TL