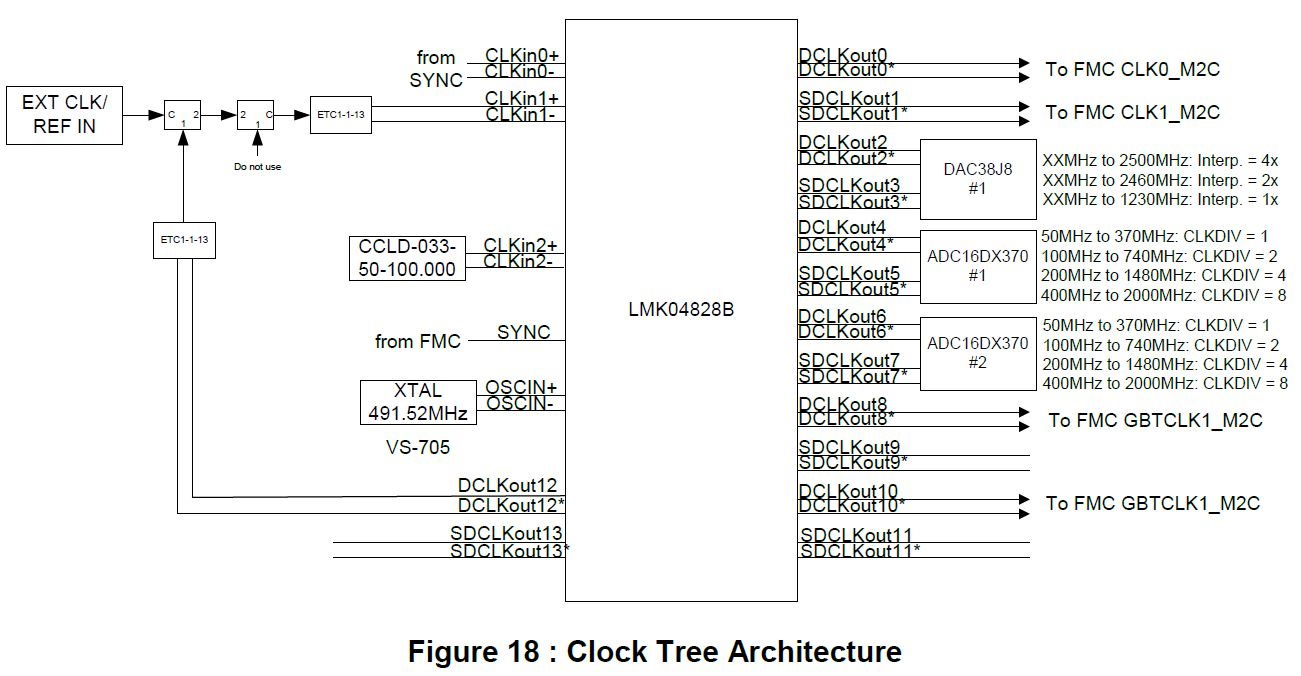

主题中讨论的其他器件:LMK04828、

尊敬的支持者:

我们的应用是 FMC144与 Arria A10 SoC 开发套件的定制集成。 没有参考设计。

我们实现了一个与 ADC16DX370s 对通信的基本 JESD 接收器。

FMC144上的2个 ADC16DX370芯片使用默认寄存器设置进行配置。 CLKIN 由 LMK04828以148.5MHz 的频率生成。

在这个启动测试配置中、FMC144输入 A2 (第二个 ADC16DX370上的 VINA)由一个14.85MHz 的3.3V CMOS 方波驱动。

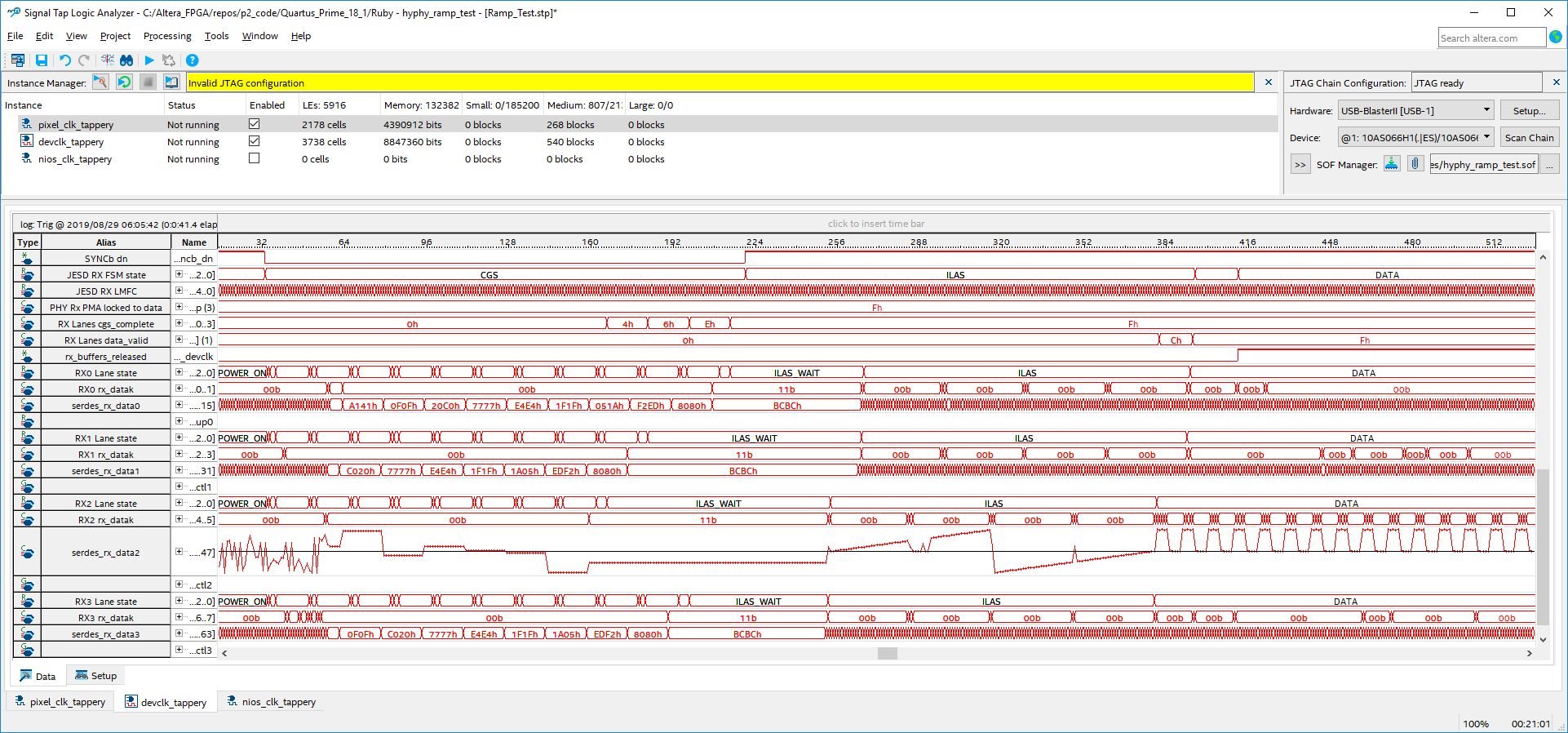

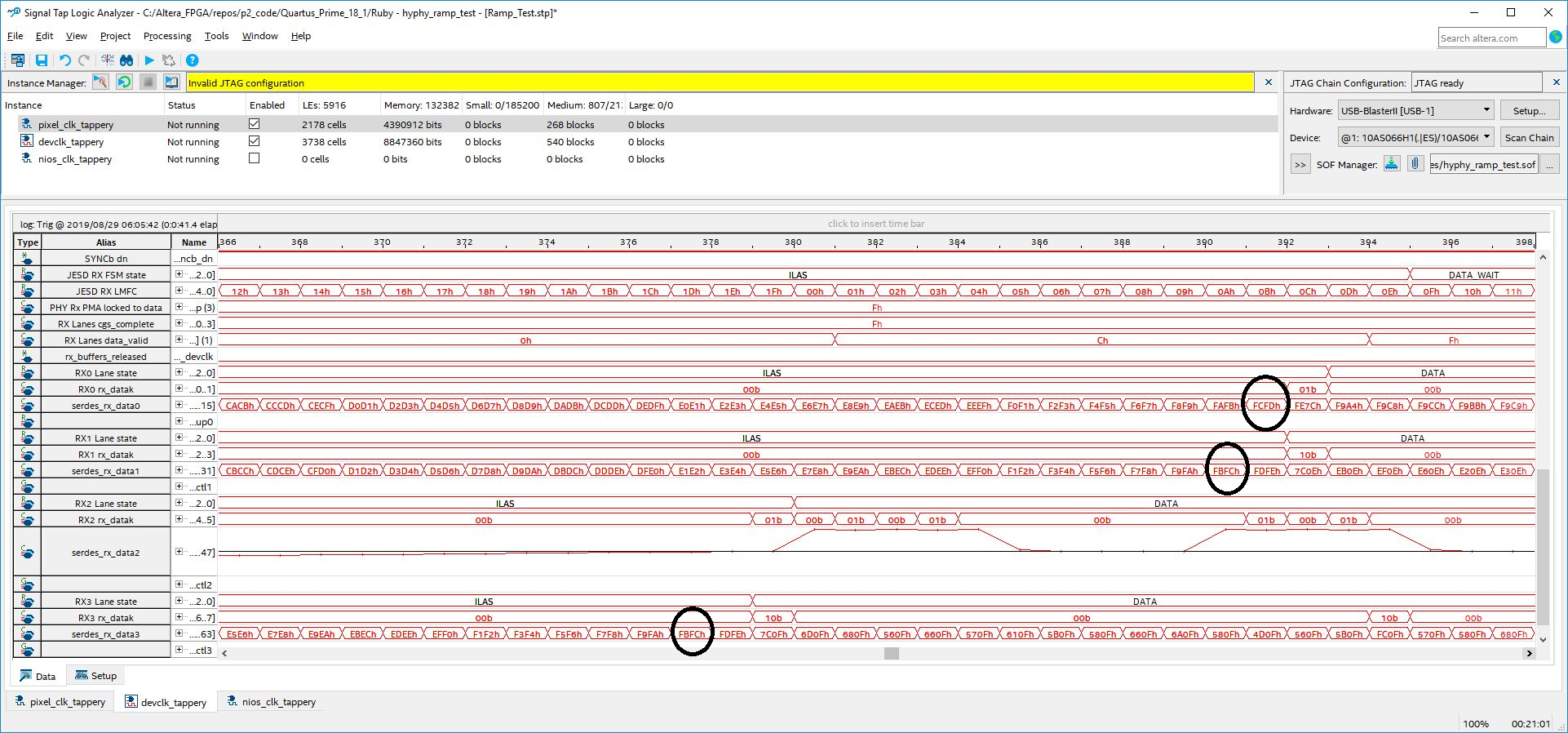

该 SignalTap 捕捉显示了 ILAS 完成后立即的预期行为:

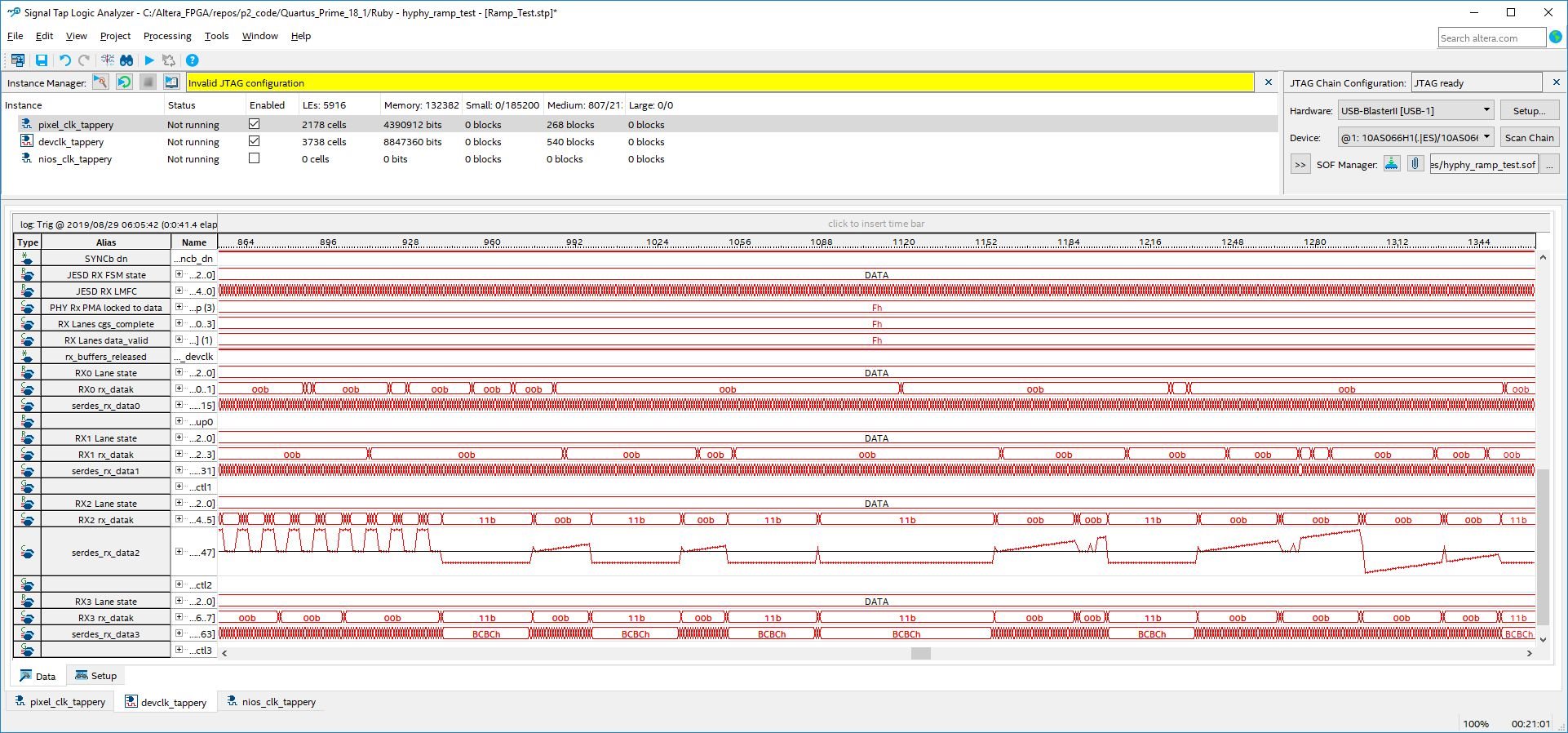

然而、即使 SYNCb 保持高电平、ADC16DX370的运行方式就像样片930周围的链路断开一样、重复发送 BCBC、然后是拉线 ILAS:

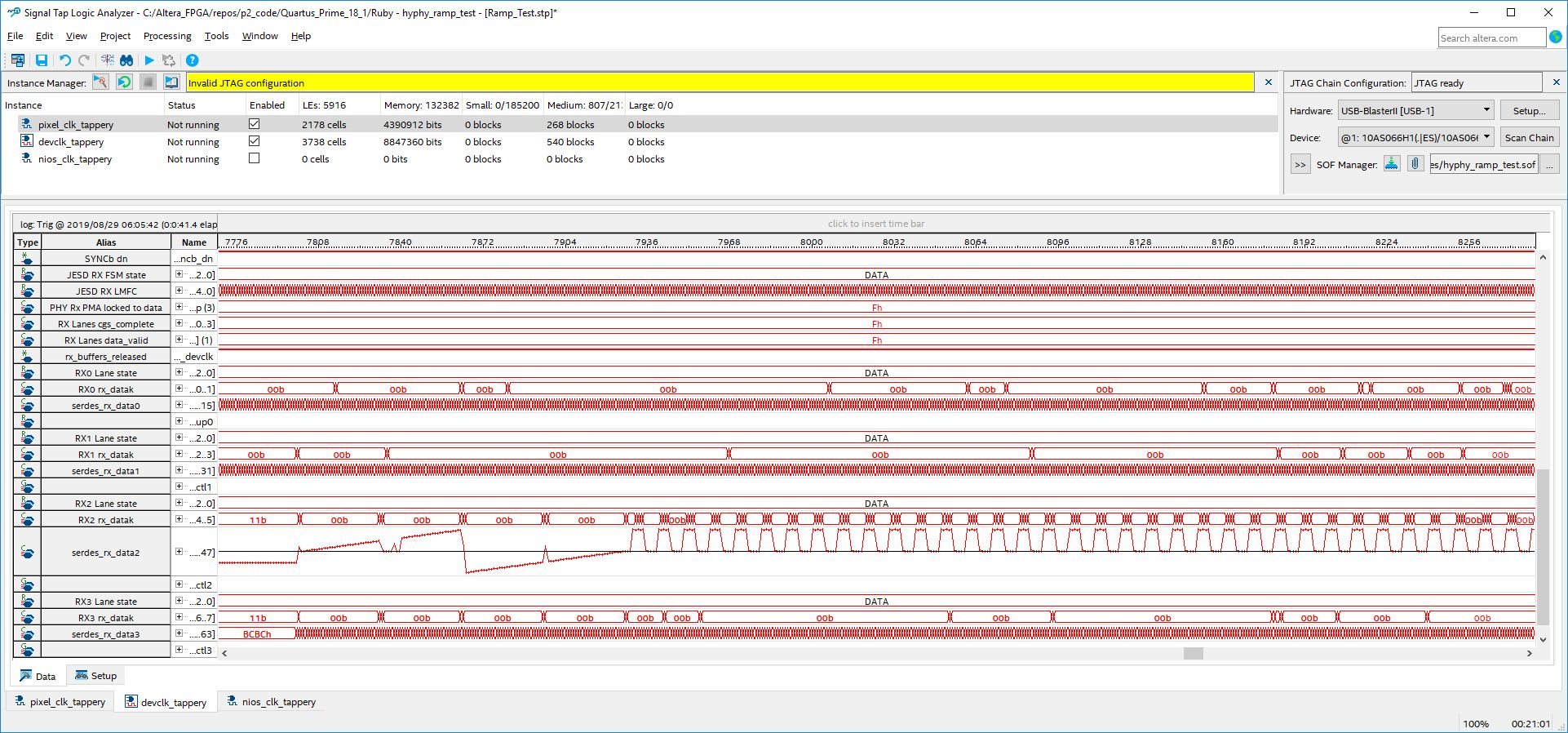

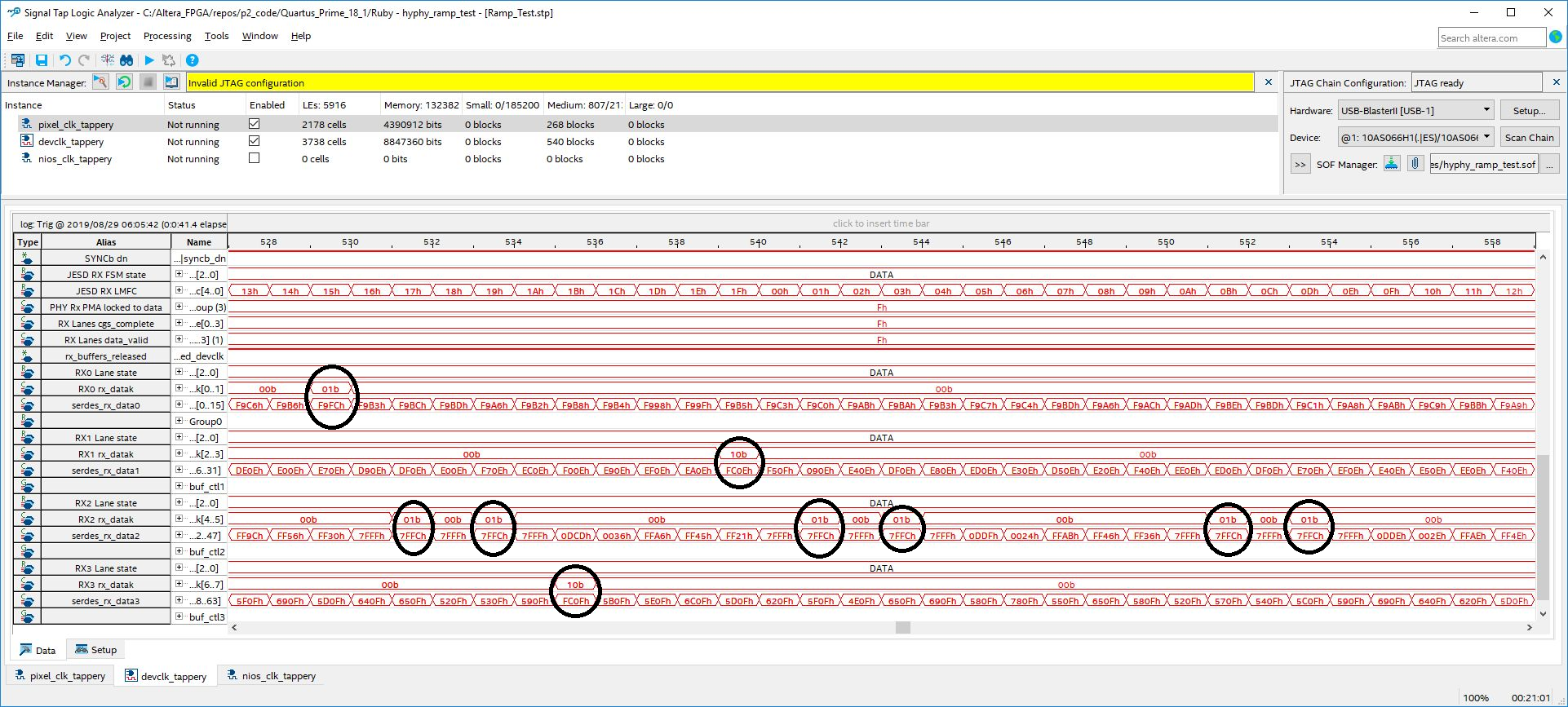

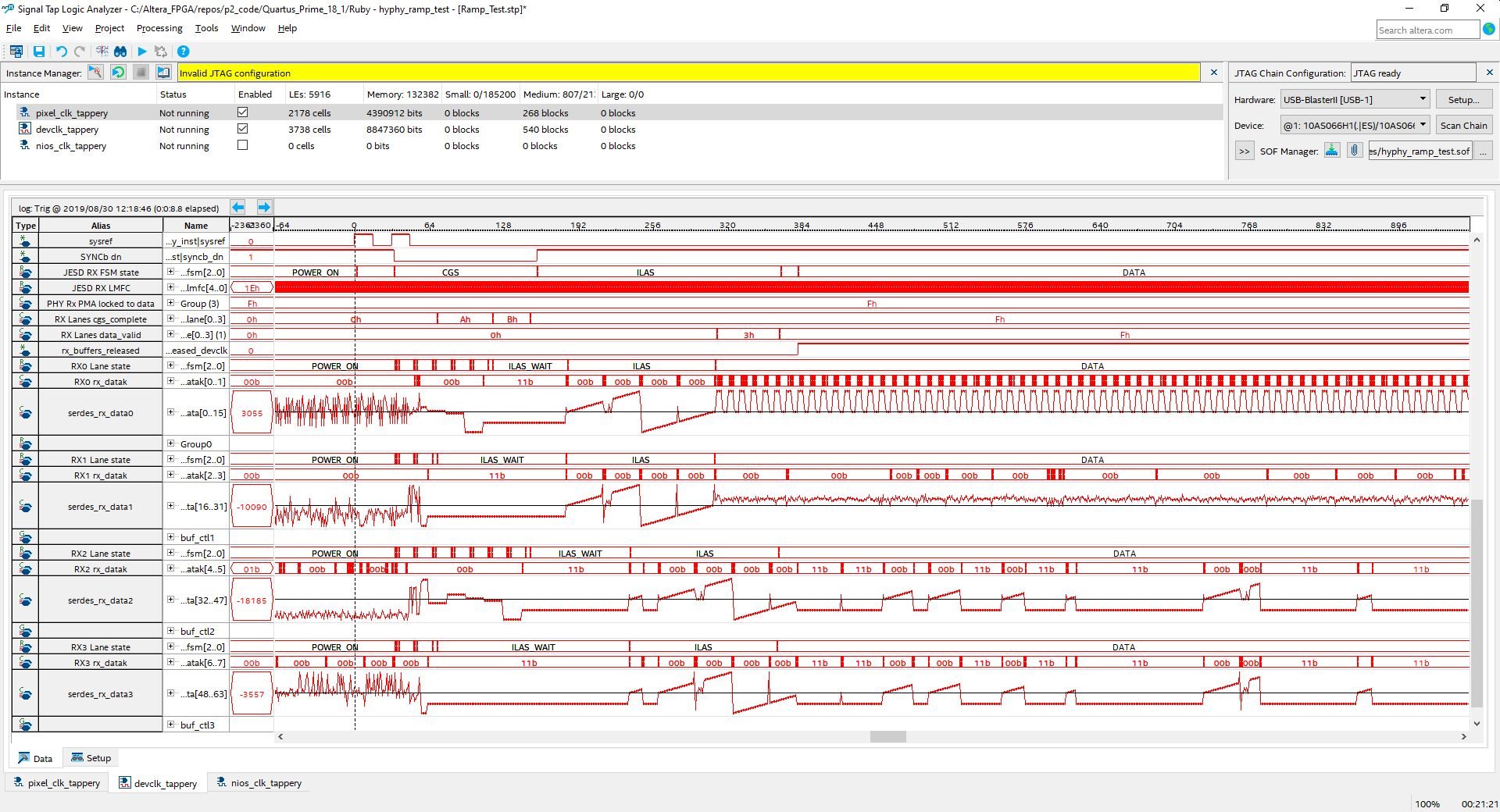

链路最终会重新建立、例如在采样7936之后:

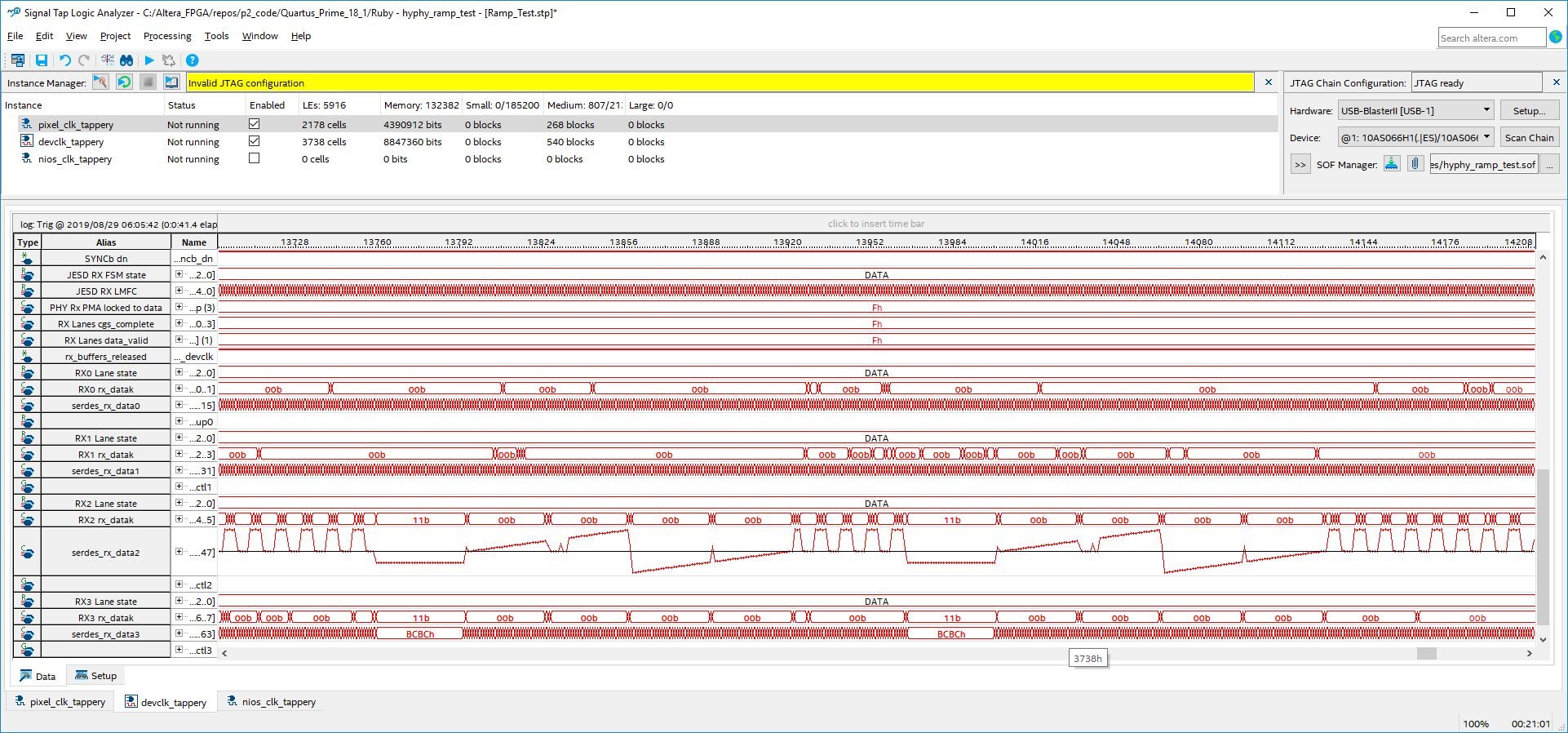

遗憾的是、此后链路间歇性中断。 下面是此 SignalTap 捕获的最后一个示例(此后、链路在超过2000个样本的时间内保持稳定、直到捕获结束):

我对这种行为有疑问

问题1:在这些情况下、ADC16DX370为什么会表现为链路断开?

Q2:只要接收器未将 SYNCb 置为有效、链路是否会在某个点之后保持稳定?

我还有关于将字节标识为控制字符的 DATAK 位的断言的问题。

此捕获突出显示了在 ILAS 期间发送的字符 FC 被正确识别为数据字节:

但是、该捕获会突出显示 FPGA 接收的字节、这些字节应为数据字节、但会对其发出数据字节:

Q3:这是数据位的预期行为吗?

Q4:JESD 接收器能否安全忽略 DATAK 位?

希望提前感谢您的回答--Todd