我有一个 ads1262配置了以下寄存器值:

1263REG[0](id)=x03

1263REG[1](电源)=x03

1263REG[2](接口)=x04

1263REG[3](mode0)=x32

1263REG[4](Mode1)=x00

1263REG[5](mode2)=x0f

1263REG[6](inpmux)=x54

1263REG[xx](ofcal)=x00000000

1263REG[xx](fsck)=x00400000

1263REG[13](idacmux)=X76

1263REG[14](idacmag)=x0a

1263REG[15](refmux)=x11

1263REG[16](tdacp)=x19

1263REG[17](tdacn)=x19

1263REG[18](gpiocon)=x00

1263REG[19](gpiodir)=xc9

1263REG[20](gpioodat)=x00

可以看出、它同时使用斩波和 IDAC 旋转、设置为38400SPS、延迟为17us、 自由运行。 我特意将2个 IDAC 幅度设置为相反的极值、以查看 IDAC 引脚上的旋转效应。

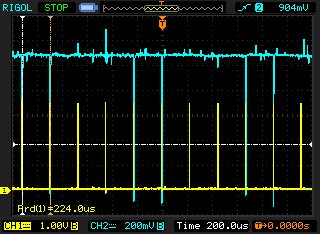

在随附的示波器屏幕截图中、CH1 (黄色)是数据就绪引脚、而 CH2 (蓝色)是 IDAC1输出。 这张照片是在我的微控制器冻结的情况下拍摄的、目的是清楚地显示 ADC 在自由运行模式下的行为。

在每次转换之前有17us 的延迟、我希望每个数据都准备就绪(207+17)= 224us、这正是我在范围内看到的结果。

现在回答问题:

1) 1)在数据表的第44页中、提到了所有后续转换的"序列重复"。 根据我获得的数据就绪信号判断、我假设重复的序列是最后2个步骤(转换3和4)。 换言之、由于我可以自由运行、因此第一个输出结果仅在我第一次发送 STARTADC 时被抑制、而不是在每个周期中。对吗?

1b)等式19和20 (第63页)在自由运行时是否重要? (我猜不会、只要我不更改多路复用器设置)

2) 2)由于 CHOP 和 Rotation 均已启用且 ADC 可自由运行、因此在任何给定时间读取的数据是否已计入最后4次测量的平均值? (第44页和第84页分别说明了这一点、每一页的平均值为2、但不包括旋转和切碎时的影响。)

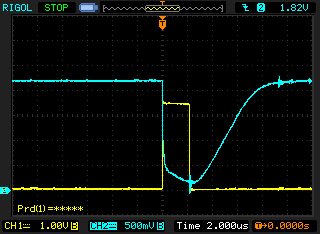

3) 3)我在 IDAC 幅度变化2us 后才获得数据就绪。 我本以为 IDAC 开始旋转后、数据就会下降224us。。。 因此、我猜对于这个特定的捕获、这个数据准备就绪实际上是指上一个周期、IDAC1为3mA。

3A)如果是这种情况、为什么 IDAC 会如此快地开始上升、从0mA 的极短周期恢复到3mA? 换言之、为什么"交换(=0mA)"IDAC1的时间长度比同相(3mA)的时间长度短得多?