Other Parts Discussed in Thread: ADS7947

我有一个使用四个 ADS7947的设计。 所有转换器共用一个公共时钟和 CS。 有一个 FPGA 生成时钟和 CS 信号并读取各个 SDO。 通常情况下、它运行良好、但有时转换器不会生成数据。 症状是所有四个转换器上的 SDO 一直处于低电平。 我怀疑 FPGA 出现了意外状态、并将转换器置于 limbo 模式、可能是32b 模式。 但是、我尝试使用 CS 高电平为芯片计时、这还不足以恢复。 如果我对32b 模式的猜测是对的,您能不能说明如何退出该模式?

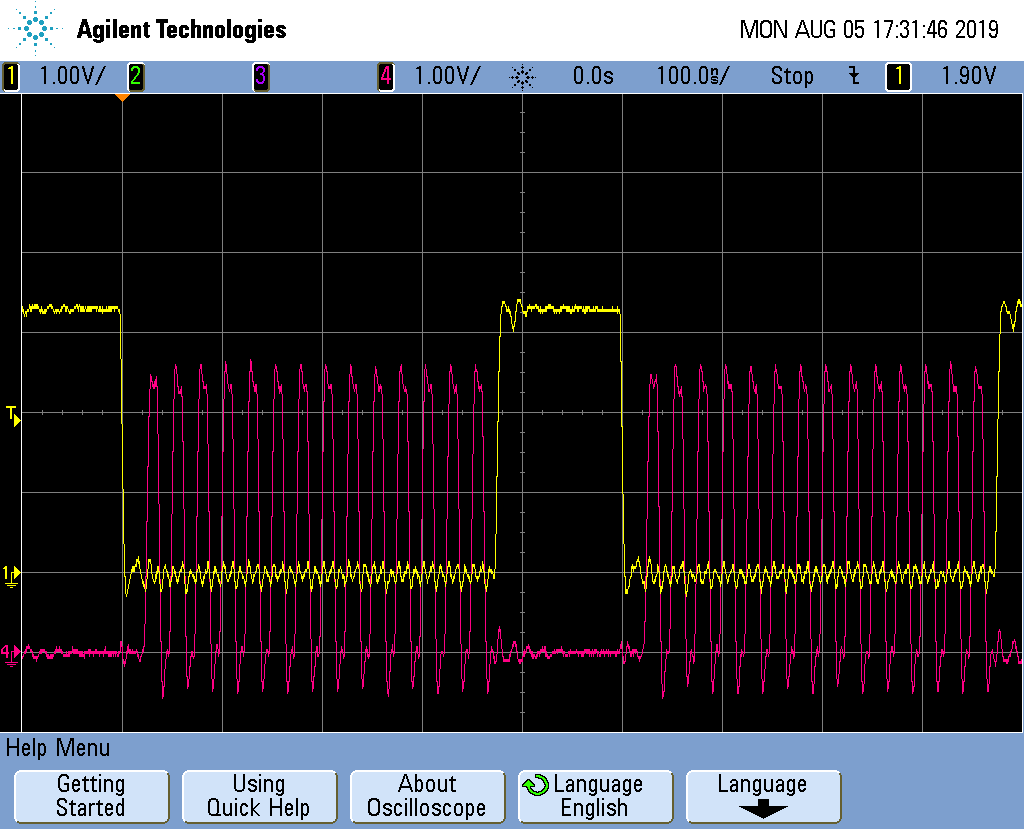

以下是有关如何使用这些器件的更多详细信息。 时钟为40MHz、占空比为50%。 CS 在380ns 下为低电平、在120ns 下为高电平。 时钟空闲、然后在 CS 置位后、脉冲14次。 CS 在第14个时钟的下降沿之后上升。 我已根据数据表检查了时序、没有发现任何违规。 此外、信号看起来很干净、没有明显的过冲或振铃。

未使用 PDEN、CHSEL、AIN1N 和 AIN1P 并将其接地。 该器件与 AVdd=5V、DVdd=3.3V、Vref=4.096V 搭配使用