Other Parts Discussed in Thread: DAC900

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC900 尊敬的先生

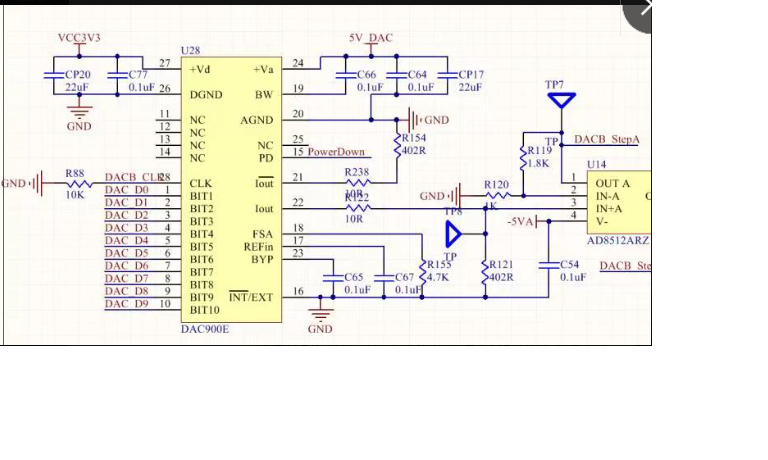

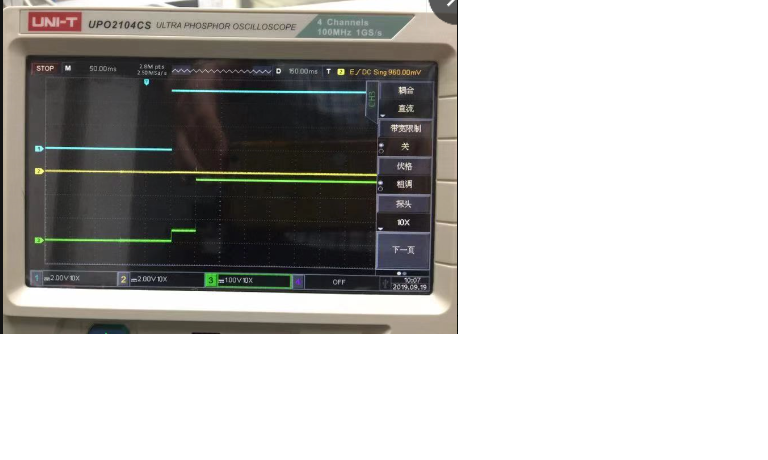

现在使用 DAC900实现电流到电压的转换、原理图如下所示;CH1是5V_DAC、CH2是 DACB_CLK、CH3是

测试点 TP8 (R121上的测试点)、我们可以看到5V_DAC 正常;当 FPGA 使用正常操作将 DAC900E (将数据写入零)复位时、TP

`s 电压在50ms 后被检测到大约0.5V、问题出在哪? 当 l 将耐 FSA 的 R155从4.7K 更改为7.5k 时,FPGA 复位

将 `s 重置为零,没有偏置电压;正确的设置值是多少? 可以帮帮我吗?