主题中讨论的其他器件: DAC3482

您好!

我们有一个板、其中 DAC3484连接到 FPGA Virtex 6。 我们将向 DAC 馈送144Msps A 和 B 通道数据(IQ)。

在初始测试中、我们将通道强制设置为 X"0000"、将 B 通道强制设置为 X"7000"。

2.插值设置为 x8

DAC 运行频率为1152MHz (来自内部 PLL)。 PLL 基准为384MHz

4、NCO 使能、NCO 输出频率从144MHz 到216MHz 不等。

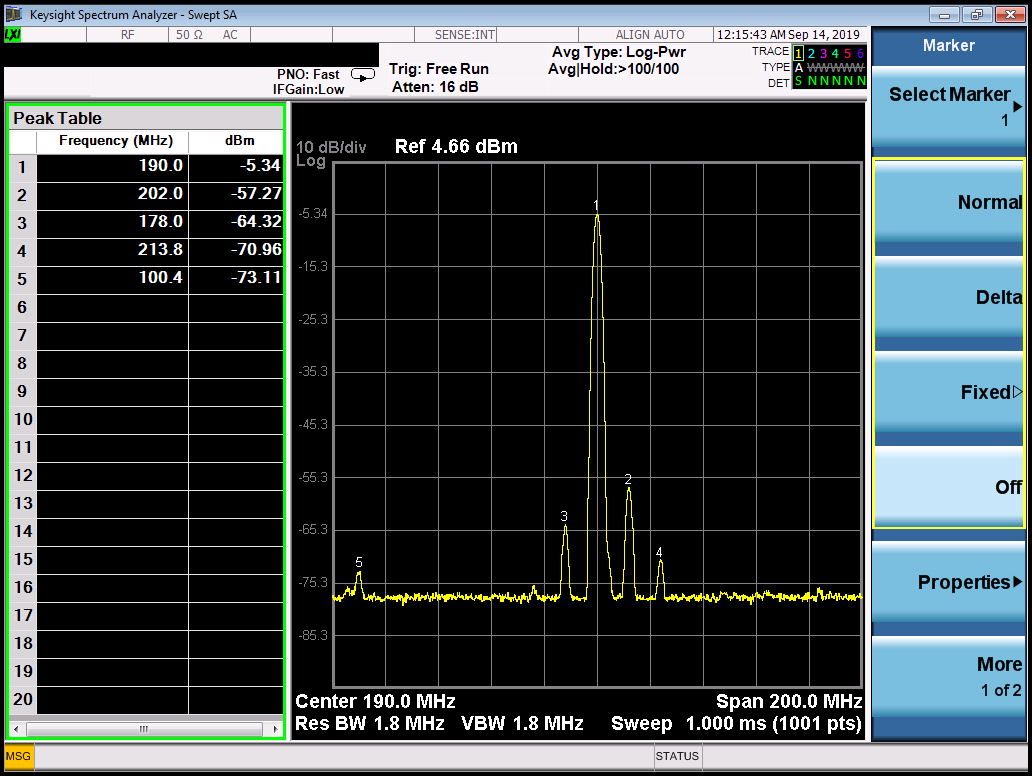

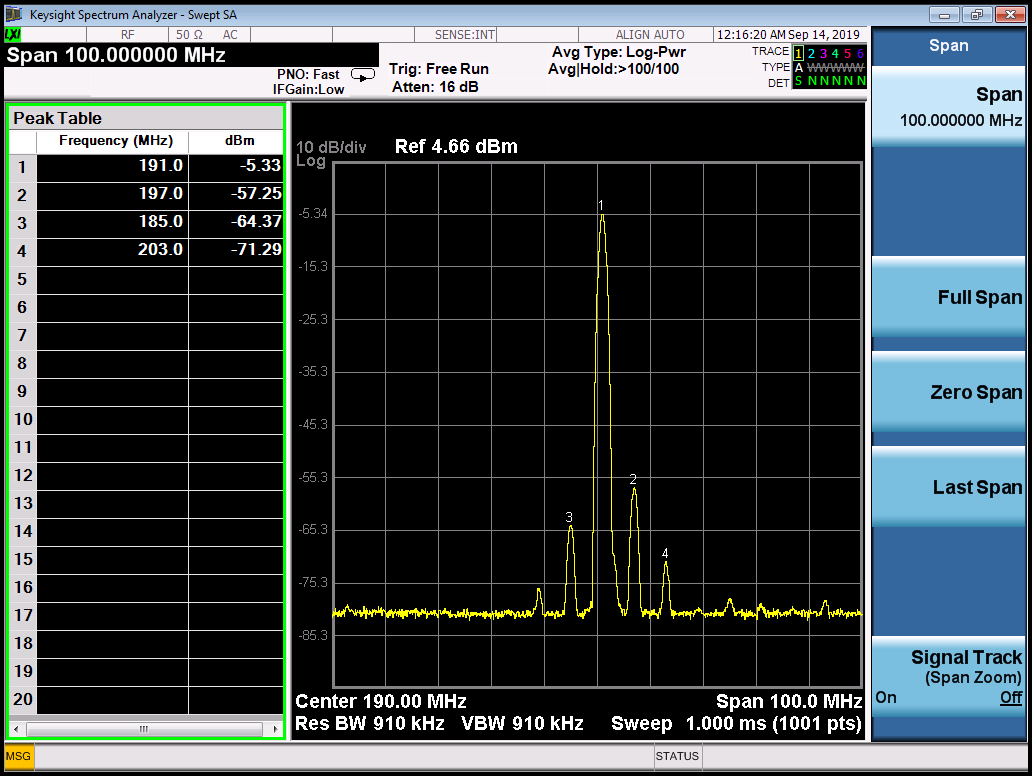

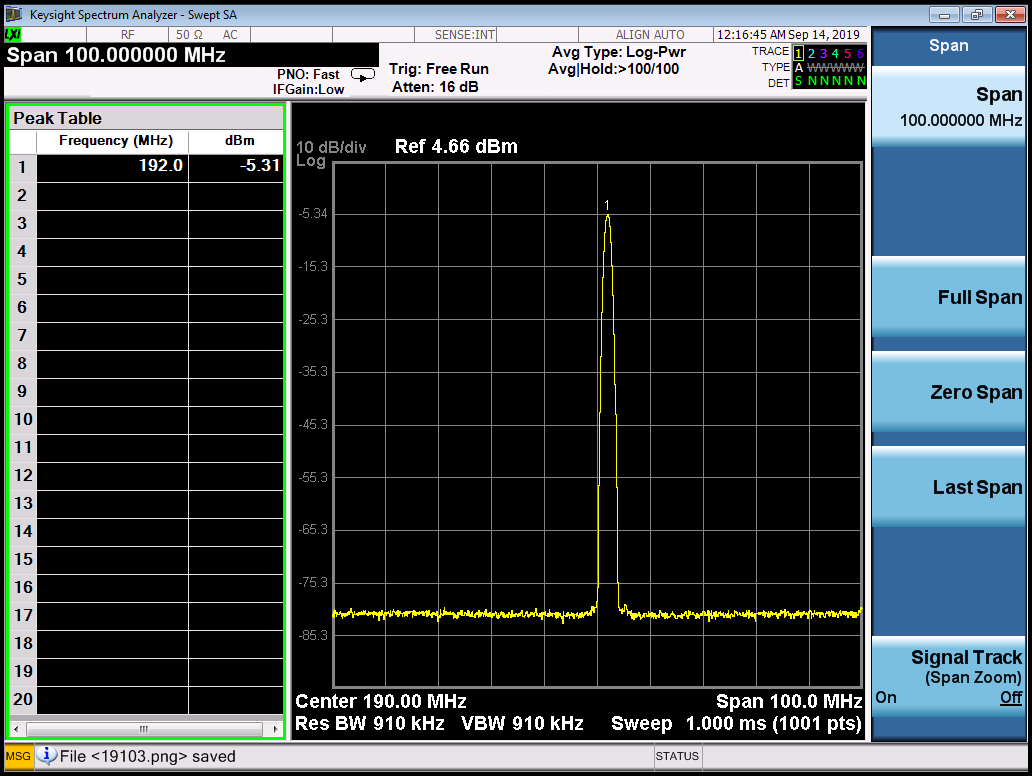

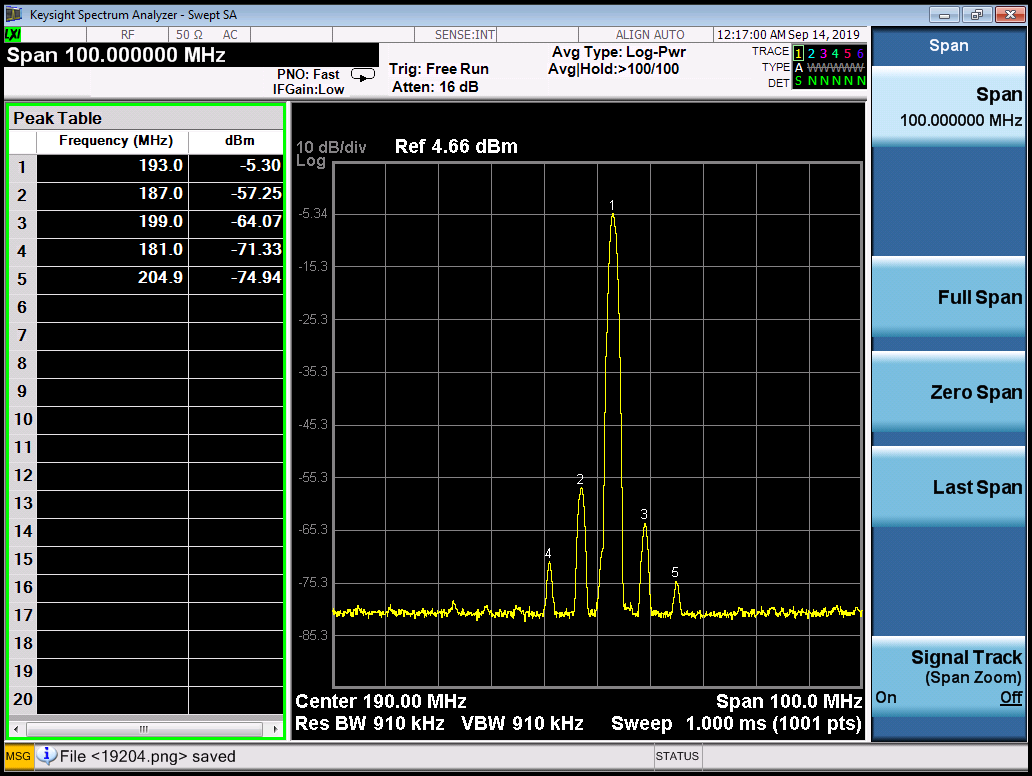

我们观察到以下行为。 @191MHz 的输出(即 NCO 调谐频率为191MHz)、我们观察到在191MHz 载波峰值附近有很多额外的频率分量。 但是、当 NCO 调谐到192MHz 时、该行为消失、SFDR 得到改善。

6.连接了不同 NCO 输出的频谱(请参阅压缩文件夹)。

这种行为背后的原因可能是什么?