Other Parts Discussed in Thread: ADS1675

您好、Keith、

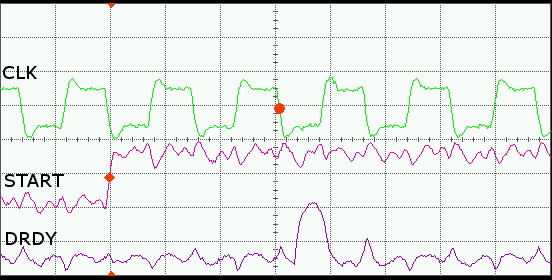

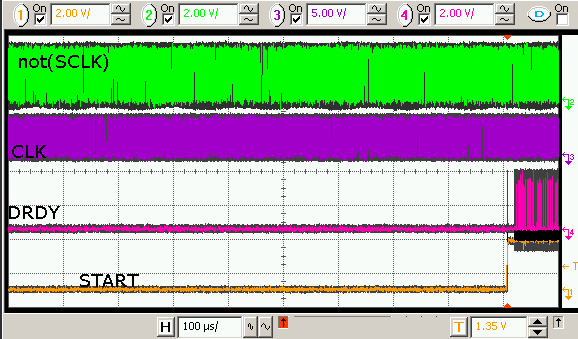

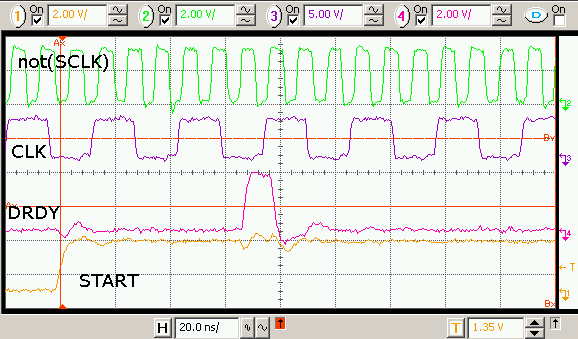

我观察到 ADS1675的未记录行为。 应用启动后、DRDY 在 CLK 的第二个下降沿附近有时会出现尖峰。 尖峰的持续时间约为 Tclk 的1/3。 实际 DRDY 的长度为 Tclk。 我的设置:DRATE = 101、高速 LVDS。 CLK 信号由 PLL 持续驱动。 这些尖峰或脉冲与 Sascha Langener 在2014年报告的“偶尔会有来自 ADS1675的额外 DRDY 脉冲”相同。

此致。