我们正在开发一个应用、希望在该应用中以3MHz 采样 ADS9224。 由于 I/O 限制、每个通道只能使用一条数据线。 这意味着我们需要使用60MHz 的时钟来计时 SDO-0/0A 和 SDO-4/0B 之外的数据。 为了在不断变化的延迟下可靠地实现这一点、我们希望使用 CRT-S-SDR 作为协议来时钟输出数据。

我在尝试使其正常工作时遇到了一个非常奇怪的问题。 在使用以下配置时、操作符合预期:

PROTOCOL_CFG (2h)= 0x20 (选择具有 SDR 的 CRT)

CRT_CFG (4h)= 0x01 (为选通输出选择 INTCLK)

output_data_word_CFG (5h)= 0x22 (屏蔽就绪输出、输出固定模式0xA55AA55A)

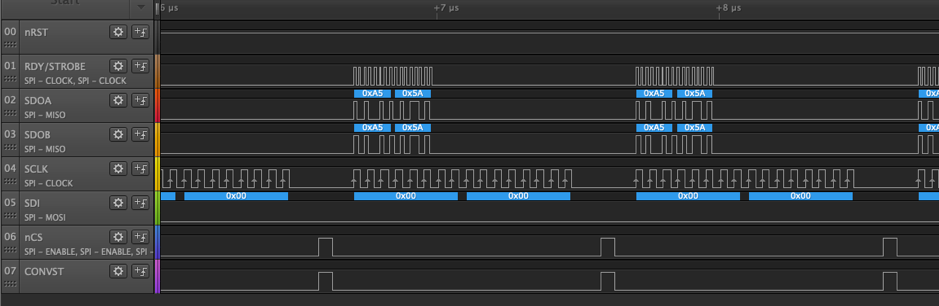

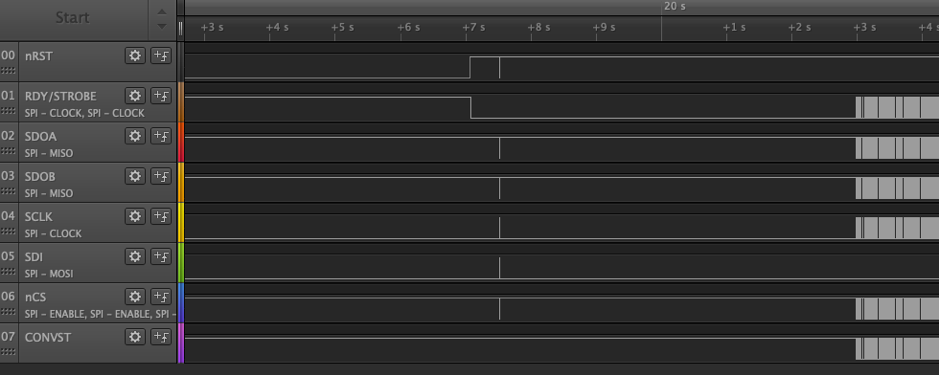

在我的逻辑分析仪上、输出如下所示(请注意、即使未使用 SCLK、我仍在生成 SCLK)、这正是我所期望的。 请注意、目前我以1MHz CONVST/20MHz SCLK 运行。

现在、当我要切换到使用 SCLK 作为选通输入来代替 INTCLK 时、我更改配置中的一个位:

PROTOCOL_CFG (2h)= 0x20 (选择具有 SDR 的 CRT)

CRT_CFG (4h)= 0x00 (为选通输出选择 SCLK)

output_data_word_CFG (5h)= 0x22 (屏蔽就绪输出、输出固定模式0xA55AA55A)

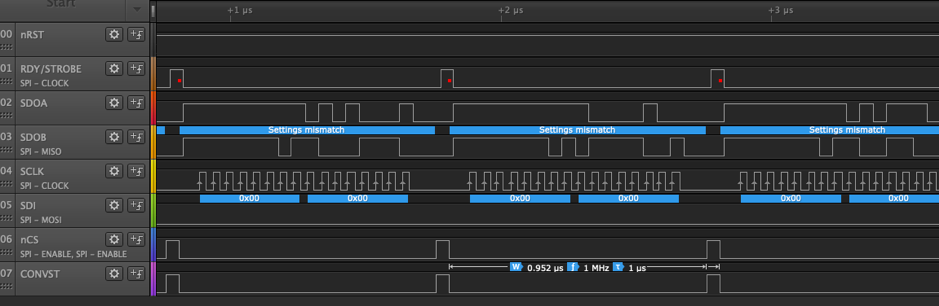

但是、现在 ADS9224R 似乎完全忽略了所有配置、并以其默认配置运行、即使用 SPI-00-S-SDR、不屏蔽就绪输出、也不输出固定模式:

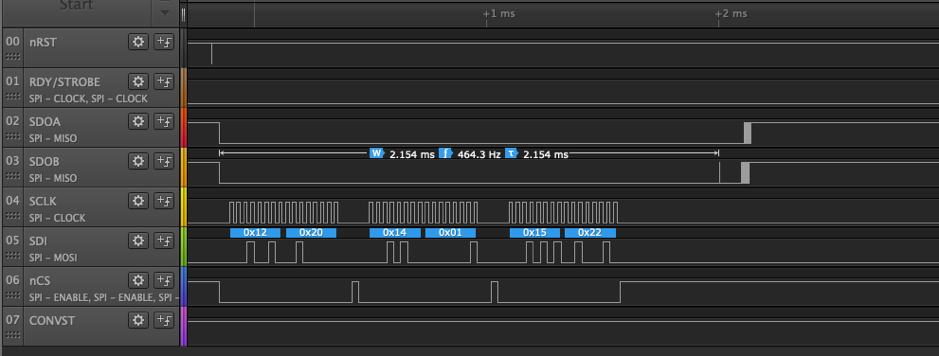

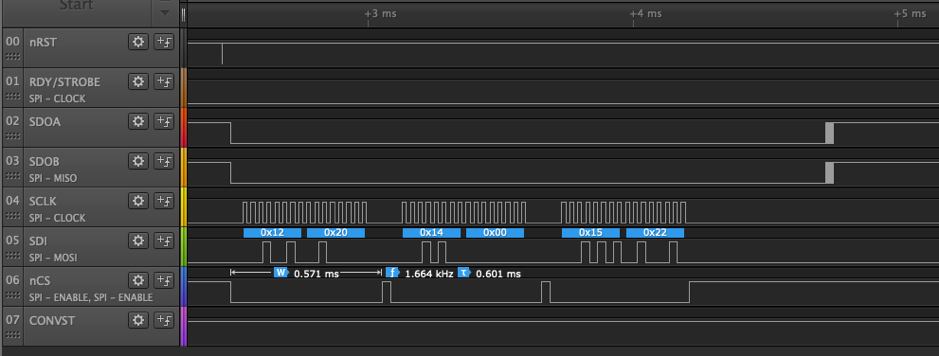

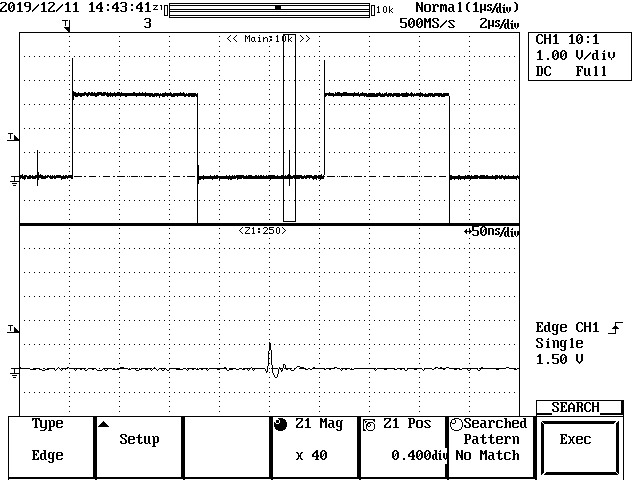

尽管配置中只有一个位发生了变化。 作为参考、下面是配置步骤的捕获(第一个位于顶部、第二个位于底部):

请注意、我在配置步骤之前切换 nRST 以清除现有配置。 脉冲的长度为450ns、nRST 脉冲和 nCS 之间有33µs μ s 被拉低以发送配置。 另请注意、配置时钟非常慢、仅为33kHz。

SDOA/SDOB 线路末端的毛刺脉冲可能是 NCS 设置为高电平时这些线路变为悬空(高 Z)的伪影。

总启动顺序如下所示:

是否有任何关于配置出错的想法? 更改 CRT_CLK_SELECT 字段中的单个位如何使 ADC 完全忽略配置? 如果有任何帮助,将不胜感激。