Other Parts Discussed in Thread: ADS54J60

主题中讨论的其他器件:ADS54J60

您好!

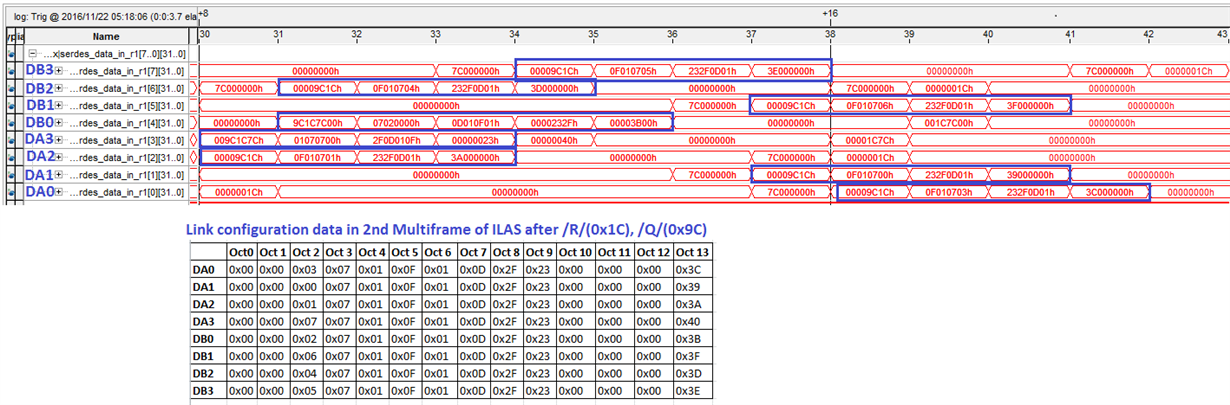

我目前使用8-2-2-4模式并设置了附加配置、希望能够帮助解决两个问题。

1.我的配置设置是否适用于8-2-2-4? 我使用本地板载振荡器作为参考时钟。

在 FPGA 端、8通道 JESD204B 接口另一端的并行数据总线为每通道256位、32位。 我目前正在尝试弄清楚通道 A 和 B 的16位样本应该是如何显示的。 我目前假设每个通道的每个32位样本都在16位边界上对齐、因此基本上一个样本位于位31-16中、另一个样本位于位15-0中。 此假设是否正确? 此外、如果我的输入信号较低且低于 FOVR 范围、我尝试打开 FOVR 以强制 LSB 为0、这样有助于更深入地了解数据表示中的任何其他潜在字节交换、但假设为16位边界、 这不起作用、我不知道它是否对齐、或者 FOVR 设置是否不起作用。

提前感谢您的帮助、

Tyler