尊敬的 TI:

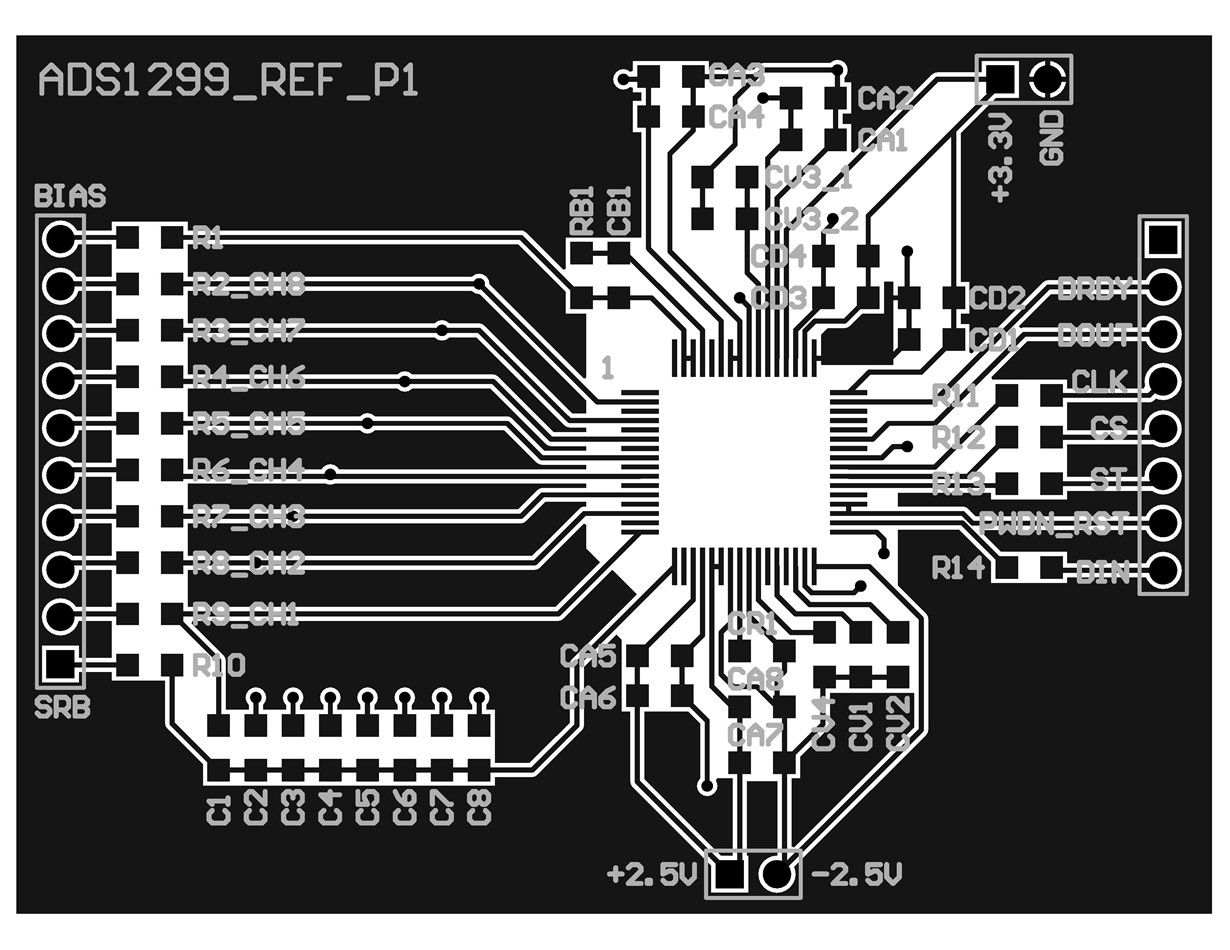

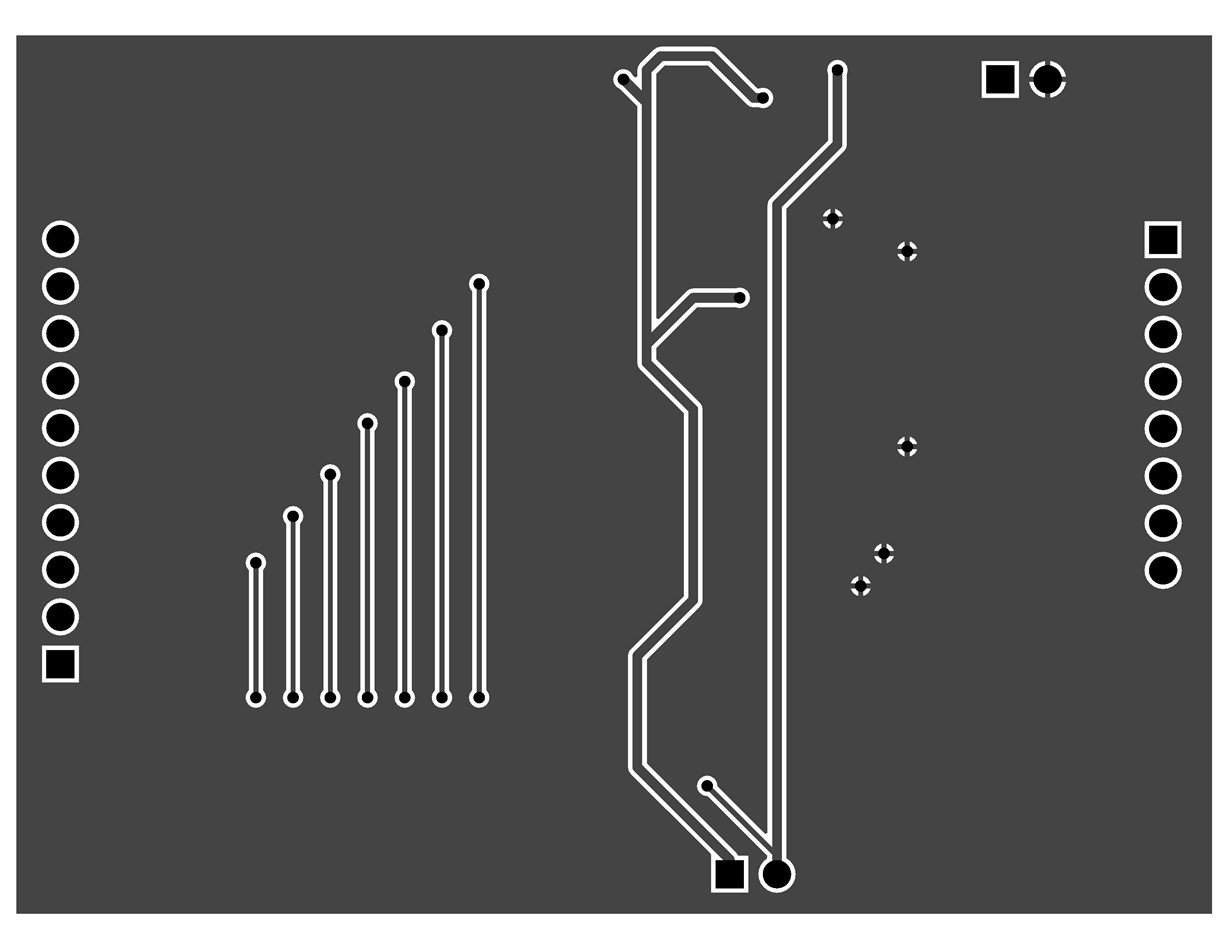

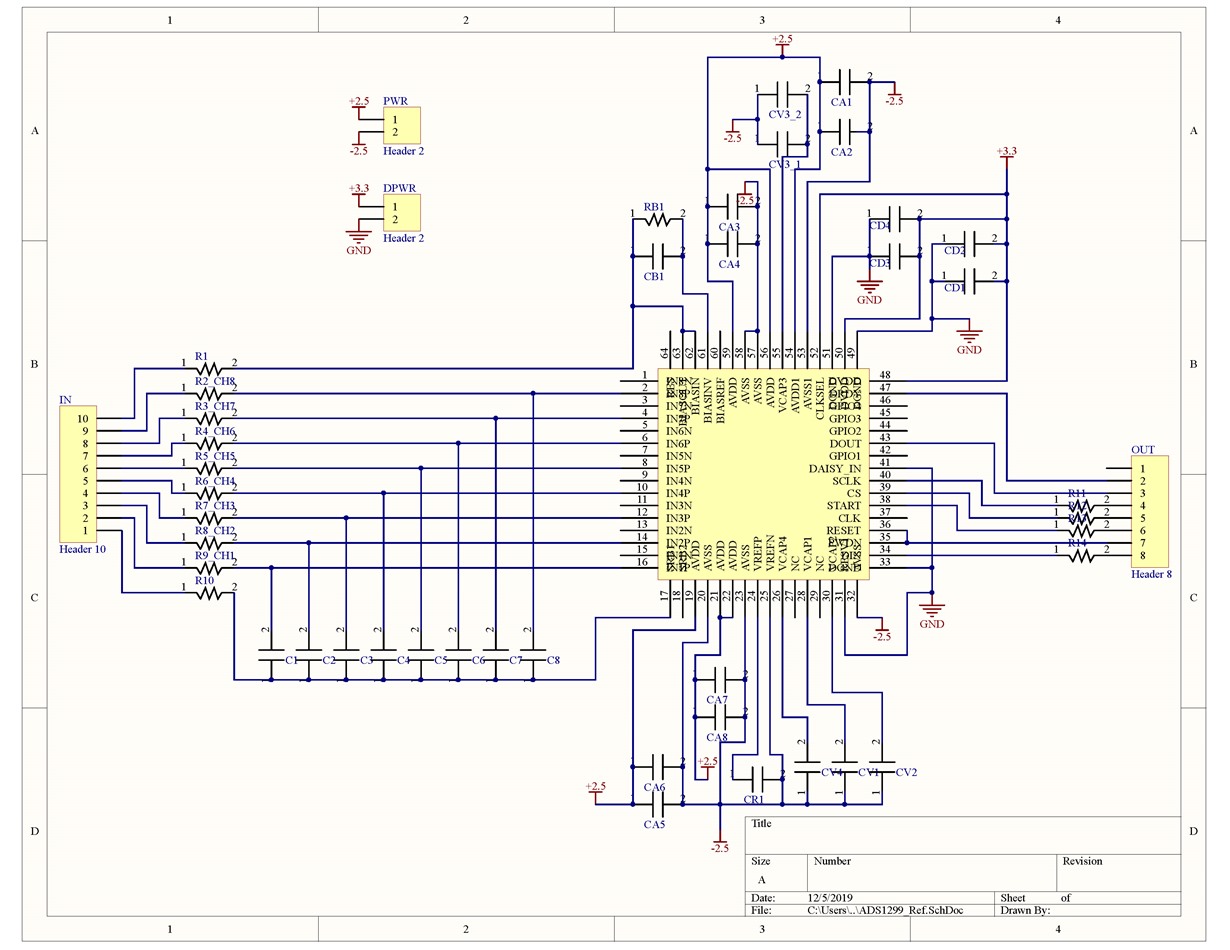

我正在尝试使用 ADS1299和数据表第73页上的布局。 (我将模拟输入更改为参考、而不是差分。)

但是、在我启动器件并发送复位命令后、数据速率大约为236.4Hz、而不是250Hz、并且一直变化+/- 0.1Hz (我在 DRDY 引脚上放置一个探针)、我还测试了大约1.94MHz 的内部时钟信号。 ID 寄存器为0xDF、这是错误的、可能是由于加电序列错误。

我认为我确实按照上电顺序:在启动前将每个输入连接到低电平、等待0.2秒、然后发送复位。 但我将4个 GPIO 引脚悬空、这是问题的原因吗?

有人可以给我一些建议吗? 提前感谢!!!