我使用 JMODE3中的 ADC12DJ5200RF-EVM 版本 B 与 Stratix 10 FPGA 连接。 JESD 链路的接收端使用 Intel JESD204B IP、该 IP 在我使用 ADC12DJ3200-EVM 时有效。 我已建立链路、K = 20、但我看到不良数据与预期样本混合。

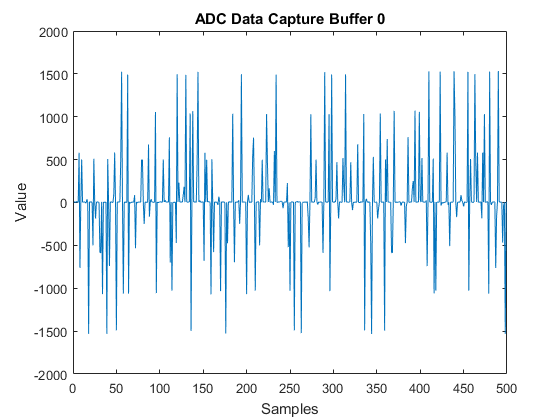

下图显示了英特尔 JESD204B 接收器 IP 输出端的数据流、链接时钟速率、传输层之前(JESD_LINK_*_DATA)和之后(TPL_DATA_*_OUT)的数据流。 这些图像是在没有输入激励的情况下捕获的、因此我希望值接近零。

信号分路器、前传输层和后传输层:

已绘制、传输后层:

我想、我的外部采样和参考时钟可能不好、但两者都共享一个常见的10MHz 基准、并且在频谱分析仪上看起来很干净。 我的采样时钟为9dBm、参考时钟为6dBm。 我不知道为什么会发生这种情况、JESD204C 协议是否会定期围绕数据发送额外的对齐字?

谢谢、

Ryan