主题中讨论的其他器件: LMK04828

你(们)好。

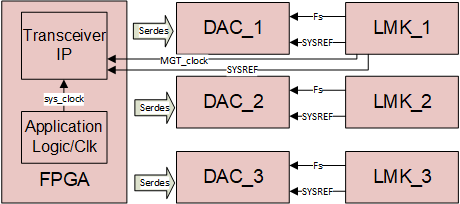

我要同步多个 DAC39J84 IC。 每个 DAC39J84由 LMK04828计时。

在 相关线程中、在执行多个 LMK 同步时、发现 LMK'输出器件时钟对齐存在±1 VCO 周期误差。

基于此、我发现在每个电源周期后、多个 DAC39J84输出未在同一位置同步、这意味着我没有实现确定性延迟。 我不确定它是否与之前的 LMK 同步问题相关。

DAC39J84的运行频率为1GHz。 JESD204B (子类1)参数如下:

L = 8 // Number of lanes M = 4 // Number of converters per link F = 1 // Number of octets per frame per lane S = 1 // Number of converter samples per frame K = 32 // Number of frames per multiframe HD = 1 // High Density N = 16 // Number of bits per sample N_prime = 16 // Number of adjusted bits per sample

我的 DAC39J84寄存器设置为:

(0x00,0x0018) (0x4a,0xff1e) (0x01,0x00a0) (0x02,0x2082) (0x1a,0x0020) (0x24,0x0020) (0x25,0x2000) (0x3b,0x0800) (0x3c,0x0228) (0x3d,0x0088) (0x3e,0x0108) (0x3f,0x005a) (0x4b,0x0700) (0x4c,0x1f07) (0x4d,0x0300) (0x4e,0x0f4f) (0x51,0x00df) (0x5c,0x1122) (0x5f,0x7654) (0x60,0x3210) (0x61,0x0001) (0x4a,0xff1f) (0x4a,0xff01)

我的问题是:我们能否实现确定性延迟并在每个电源周期后同步多个 DAC39J84 IC、而 LMK 器件时钟是否存在±1 VCO 周期误差?

我曾认为、如果我们可以确保 SYSREF 对齐 LMF、±1周期器件时钟误差在 JESD204B 协议中不是主要误差。

您能否帮助检查 DAC39J84寄存器设置中是否缺少任何内容?

谢谢、祝您一切顺利、

Yilun