您好!

我正在尝试了解如何配置安装在 TSW3XJ8XEVM 上的 DAC38J84、以便 在四个通道上产生1228.2MSPS、因此基本上是可能的最大数据速率规格。

我选择使用 TSW3XJ8XEVM GUI

DAC 输入数据速率= 1228.2

内插= 1

SERDES 线路数= 8

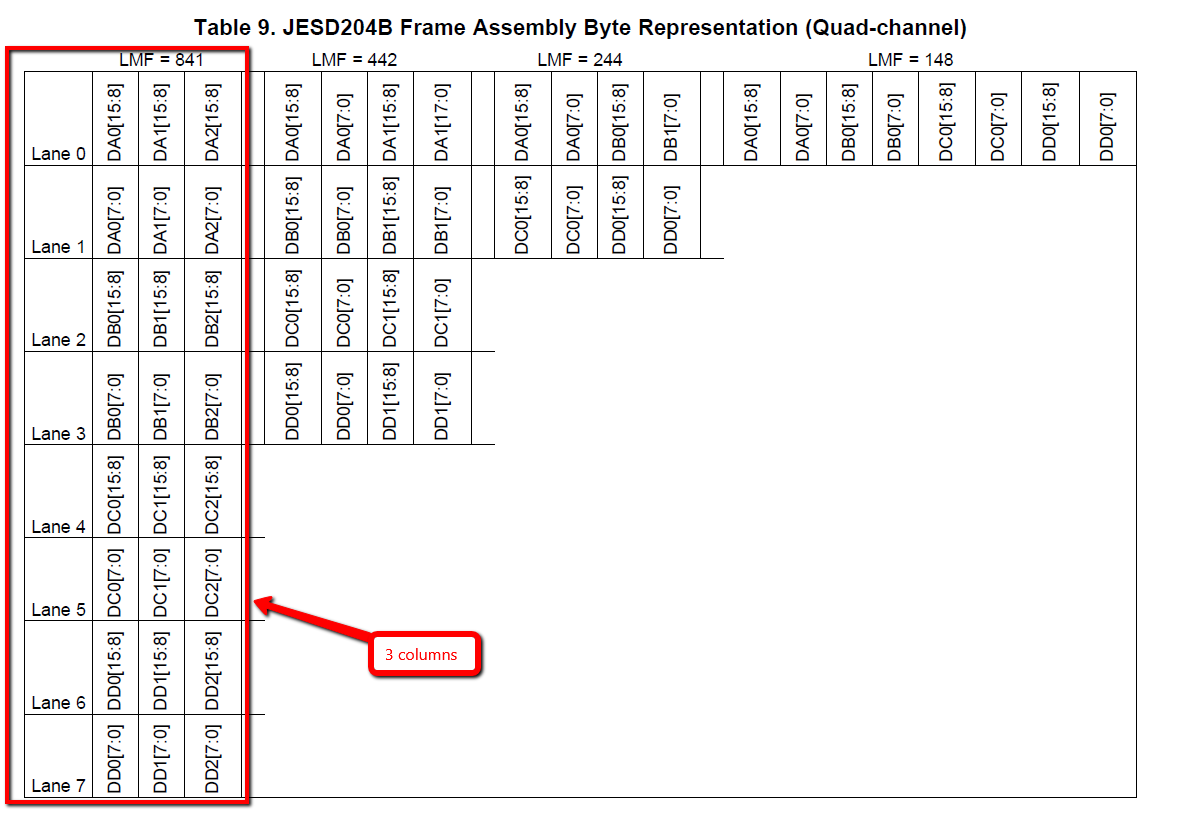

我假设 DAC38J84手动(表9)配置 LMF = 841是我正在使用的配置(在 GUI 的 DAC JESD 块选项卡中确认)。 让我感到困惑的是通过 JESD204通道进行传输的图示、DAC38j84手册的表9对此进行了说明。

我的假设是、在一个帧中:

通道0转换器 A 的 sample..2的最高有效8位被传输。

通道1转换器 A 的 sample..2的最低有效8位被传输。

接下来、我假设一个帧持续4个 FPGA 时钟周期。 我希望在1个 FPGA 时钟周期内(307.2MHz)、每个转换器传输4个样本、但该表仅显示每个转换器3个样本。 因此、我无法理解如何实现数据速率。

此致

Blaz Kelbl