主题中讨论的其他器件: ADC3542、 ADS4146

您好!

我们使用的是 ADS4149。 ADC 输入信号频率范围为328Mhz 至335Mhz。 我计划通过考虑7MHz 的输入带宽来使用24MHz 作为采样频率。

对于该频率范围、数据表显示 SNR 为预期值69dB。 如果我使用24MHz 作为 FS、它会因为欠采样而降低 SNR 吗?

如果是、请告诉我 SNR 会受到什么影响、以及由于折返(别名)可能会降低多少。

谢谢

Vetri

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们使用的是 ADS4149。 ADC 输入信号频率范围为328Mhz 至335Mhz。 我计划通过考虑7MHz 的输入带宽来使用24MHz 作为采样频率。

对于该频率范围、数据表显示 SNR 为预期值69dB。 如果我使用24MHz 作为 FS、它会因为欠采样而降低 SNR 吗?

如果是、请告诉我 SNR 会受到什么影响、以及由于折返(别名)可能会降低多少。

谢谢

Vetri

您好、Vetri、

我们可以让有人在实验中以该采样率在 EVM 上检查性能、但可能需要几天时间才能获得结果。

我可能建议查看 ADC35xx 器件系列。 这些是单通道、超低功耗器件、包含集成的 NCO 和降压转换器。 我建议从 ADC3542开始。 您可以通过访问此链接并在搜索框中输入"ADC35"来查看所有这些器件。 https://www.ti.com/data-converters/adc-circuit/high-speed/products.html

此致、Chase

您好、Vetri、

我们手头上有一个 ADS4146、这是一个非常相似的器件、其额定频率为160MHz 而非250MHz。 我们能够使用160MHz 和24MHz 的采样频率和7MHz 的输入频率对其进行测试。 我们在采样频率和输入频率中都有滤波器。 这是为了在基带测试器件、但如果我理解正确、您希望使用大约330MHz 的输入、该输入将处于27奈奎斯特?

结果显示在随附的 PowerPoint 中、您可以看到 SNR 和 SFDR 没有显著变化。 它实际上通过使用较低的采样频率得到了改进。

希望这能解答您的问题。

最棒的

Camilo

您好、Vetri、

我们使用 ADS4146重复了测试、但这次使用331MHz 输入频率。 结果显示在随附的 PowerPoint 中。 但 SNR 确实会更低。 通过将采样频率从160MHz 更改为24MHz、我们将损失大约6dBFS 的 SNR。 采样频率为24MHz 时、您将在27奈奎斯特区域工作、这意味着您需要确保对输入进行滤波、以便基带和输入之间的所有噪声不会折返到基带并出现在捕获中。

重申 Chase 的说法、最好查看 ADC35xx 器件系列。 因为它们具有集成的可编程 NCO 和降压转换器。

希望这能解答您的问题。

最棒的

Camilo

您好、Camilo、

我在定制板中使用的是 ADS4149 ADC。 ADC 采样时钟由 FPGA 驱动。

采样频率(fs)= 24MHz

ADC 输入信号频率(Fin)= 328MHz

ADC 输入信号功率级别=-10dBm。

FPGA 器件型号:MPF200T

我将通过 FPGA 将 OCXO 时钟(24MHz)路由到 ADC、作为 FS。 我可以在 ADC 输出端看到8MHz。

问题1陈述:

现在、我将通过 FPGA 的内部 PLL 而不是 OCXO 生成相同的24MHz 时钟、并以 FS 的形式路由到 ADC。 ADC 输出本身不正确。 预计为8MHz、但仅存在 junks。

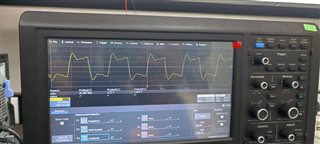

我已经用示波器探测了 ADC 时钟信号、可以在 OCXO 时钟和 FPGA 的内部 PLL 时钟之间做出以下改变。

OCXO 时钟的范围为-0.2V 至+1.5v、过冲为0.4v (附件 OCXO_AS_ADC_FS)

内部 PLL 时钟的范围为-0.3V 至+1.7V、过冲为0.5V

从 ADC 数据表中可以看出、LVCMOS 单端配置的时钟信号最大电压为1.8V。 我们使用相同的 LVCMOS 单端配置。

我可以看到内部 PLL 时钟超过1.8V。 请告诉我、问题是由于这个问题而发生的?

问题2:

ADC 时钟在 ADC 输入信号中耦合。 基波为328Mhz。 由于 ADC 时钟耦合、我们看到基频降低了352MHz、376MHz 和400MHz @23dB。

请提供建议以消除此耦合问题。

注意:此处附上了 ADC 部分原理图。