主题中讨论的其他器件:LMK00304、 TPS22917

您好专家、

我不熟悉 ADC 器件、客户对器件应用有几个问题、请在下面找到问题、

ADC09xJ1300的输出引脚:D8-+、D8-... 这些引脚的用途是什么? 如何区分 A、B、C、D 的四个通道、这些通道的结果是否反过来输出?

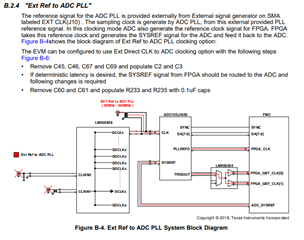

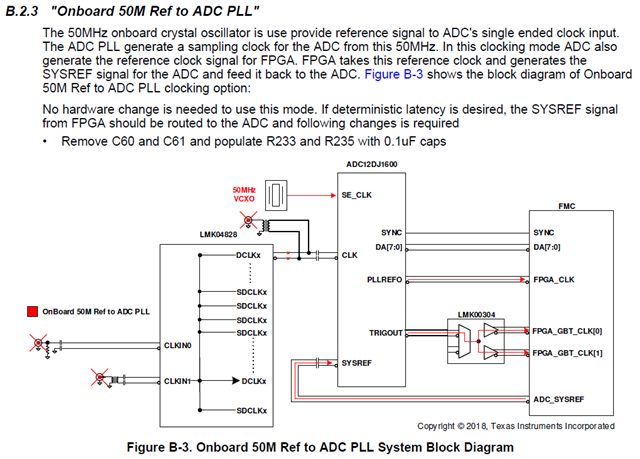

2.客户想要使用以下参考设计、是否可以移除50MHz VCXO 并使用 FPGA 的内部 VXCO?

3. 从 上面的图 B-3中、是否可以移除 LMK00304? 这有什么作用? 其他引脚同步、SYSREF、PLLREF0的功能是什么? 需要 FPGA 提供哪些信号?

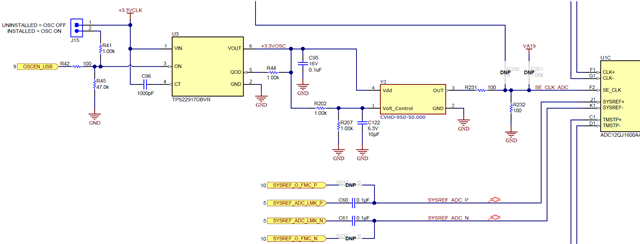

从下图中可以看到、如果 Y2始终正常工作、TPS22917是否是必须的?

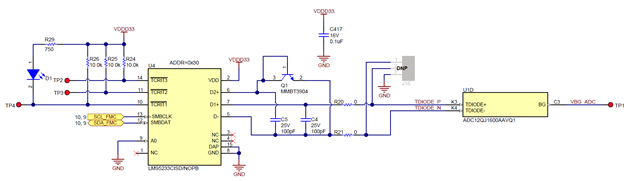

5.当温度超过目标值时,TDIO+/-如何工作?

感谢你的答复。

此致、

布莱斯