主题中讨论的其他器件: ADS1292R、 ADS1292

你(们)好

我正在使用 ADS1291和 nRF52832进行开发。

我对时钟设置和数据噪声有疑问。

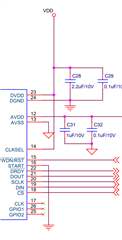

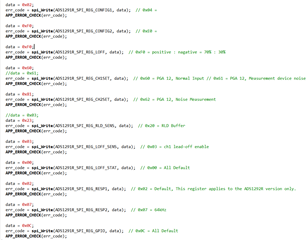

首先、我的电路图和 ADDR 设置。

- CLKSEL = 1、AVDD = 5V、我不使用 CLK 引脚

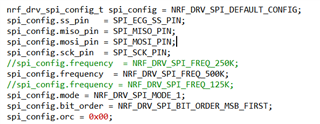

- 只使用 SCLK 引脚、 但是 SCLK 是 SPI 时钟、我知道它不涉及芯片时钟(对吧?)

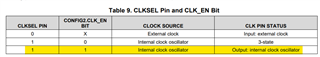

问题1. 如果 CLKSEL 引脚= 1、CONFIG2.CLK_EN 位= 1、时钟源和 CLK 引脚状态都使用内部时钟振荡器。

那么、基本而言、您意味着内部时钟最高可支持128KHz 吗?

然后、是否应用了 CONFIG1.DR2~DR0设置的数据速率值?

示例 CONFIG1 = 0x02 (500SPS)= 500Hz

30秒测量时的数据为15000

如果上述内容正确、我不知道 CLK_DIV 发挥什么作用。

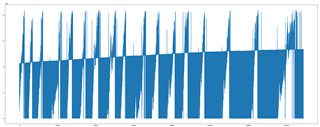

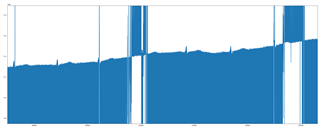

问题2. 测量数据时是否会产生大量噪声?

像图片中一样、数据上有太多噪声、我不知道原因

谢谢你。