主题中讨论的其他部件:ADS54J40、 ADS54J40EVM、 ADS54J60、 ADS41B49、 LMK04821、 LMK04208、 LMK04828

尊敬的专家:

我的客户正在考虑采用14至16位和1Gsps 的系统。

如果您能提供建议、我将不胜感激。

--

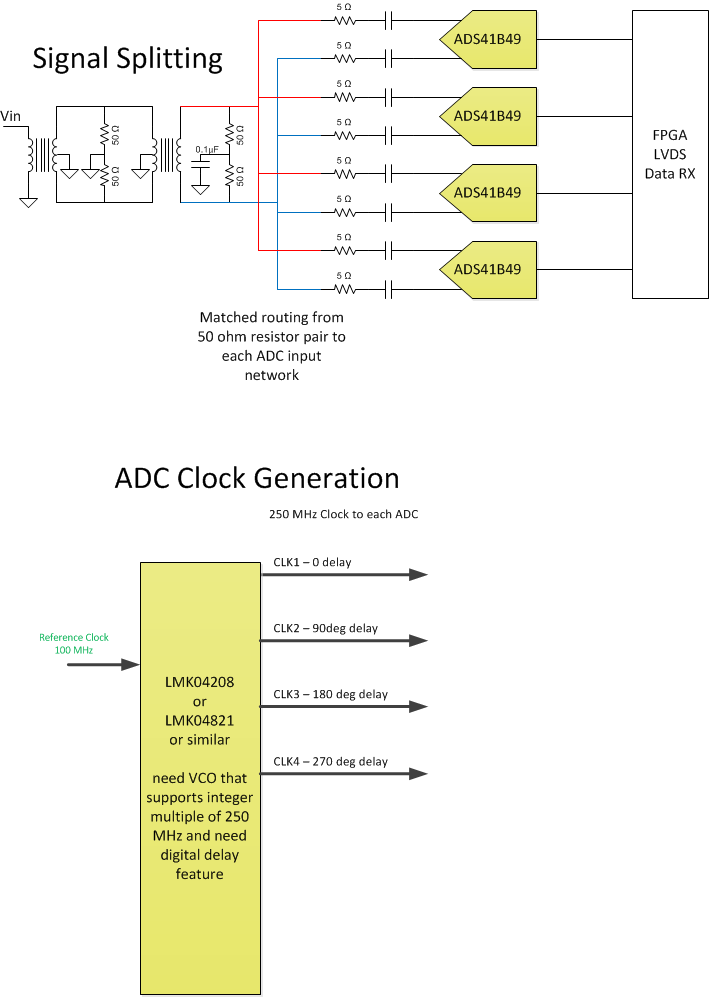

由于基板的生产存在限制、因此需要实现并联 ADC。

我想使用 SLAU247这样的 Interleave、是否有任何符合上述条件的参考设计?

为了实现1GSPS、我认为将使用四个250MSPS 器件。

我希望您将其与模数转换器一起提出。

--

感谢您提前提供的出色帮助。

此致、

新一