主题中讨论的其他器件: ADC12J4000

您好!

我们的原始 FPGA (Xilinx KU060)板通过 FMC 结合了 ADC12J4000EVM。

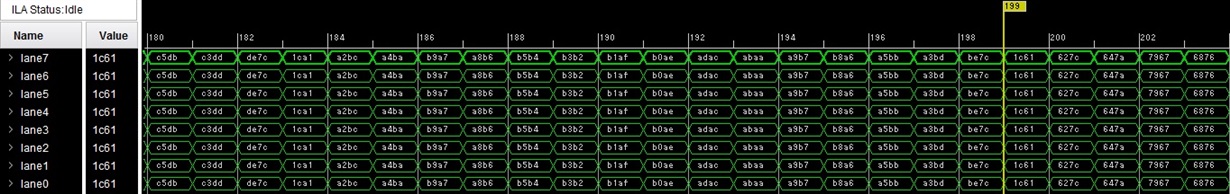

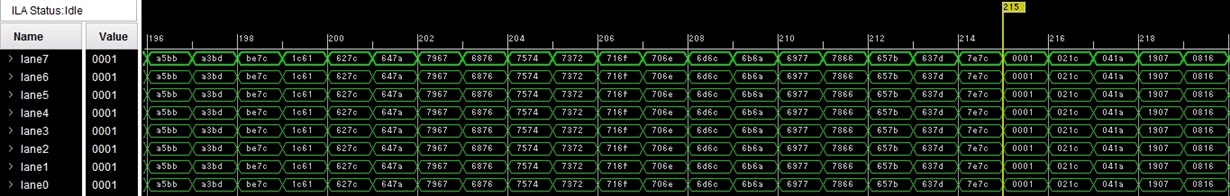

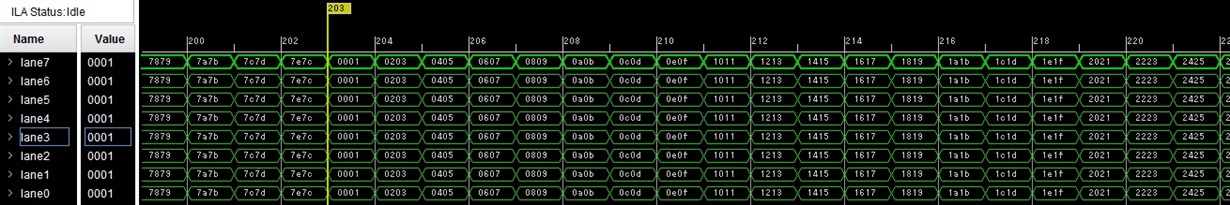

我正在使用 FPGA 上的 ChipScope 检查从 ADC12J4000 (JESD204B)接收到的数据。

Ramp_Test_Data 似乎不正确。

我可以在 ILAS 数据上看到适当的 K_symbols、

但我无法确认 ILAS 上的 Dx.y_data 每个帧数据是否正确。

Dx.y_data 是否等于 Ramer_Test_Data?

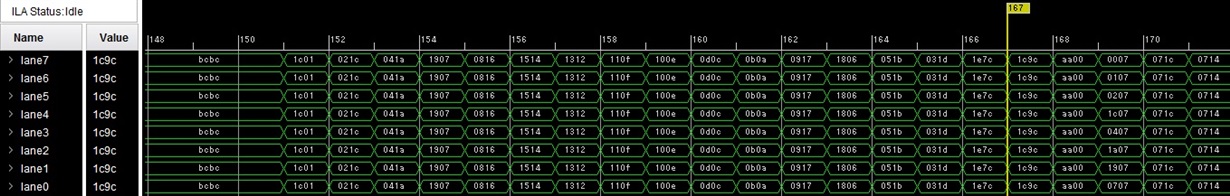

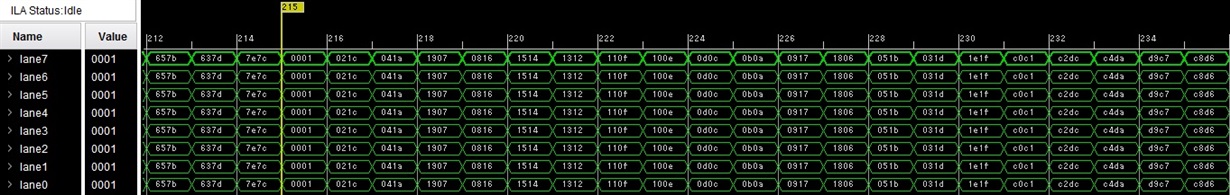

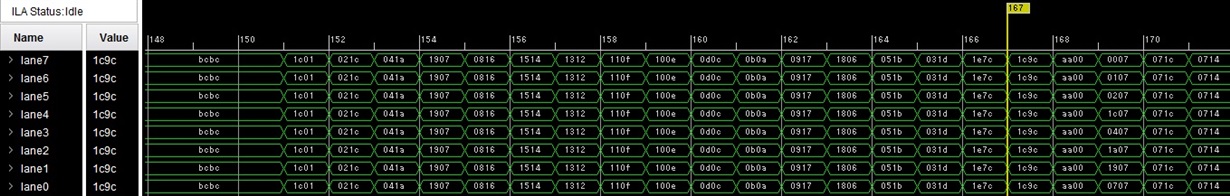

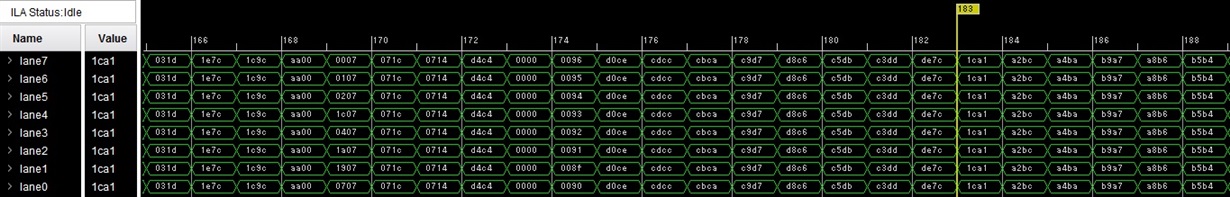

我附加 FPGA 收发器的 rxdata 的 Chipscope 数据。

那么 、ILAS 数据是否正确?

如果没有 、请告知 ILAS 上的正确数据(位)和用户(Rams_)数据。

[我们的系统配置]:

ADC12J4000:LMF=8、8 (旁路、无抽取、DDR)、FS=3.2GSPS (Line_RATE =6.4Gbps)

FPGA 上的 JESD204B:GTH_收 发器(不使用 JESD204B_IP) 16位数据总线

在 ADC12J4000上运行 Ramp_Test_data

[ILAS 数据]

我使用 GUI 将"0x55"设置为 JESD_DID (0x203)寄存器、但可以看到上面的"0xAA"。

[斜坡_测试_数据]

00、01、02、1C?、04、 1A?