主题中讨论的其他器件: ADC12DJ3200、 DAC39J84、 LMK04828

大家好、

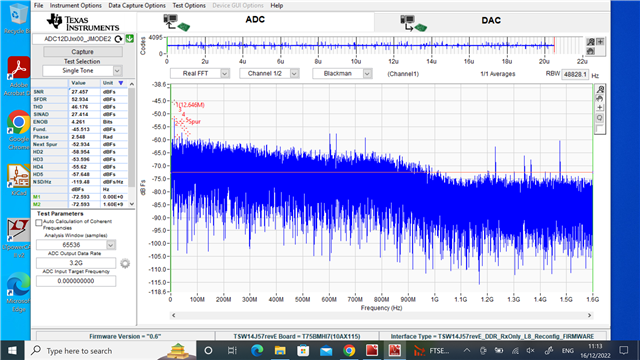

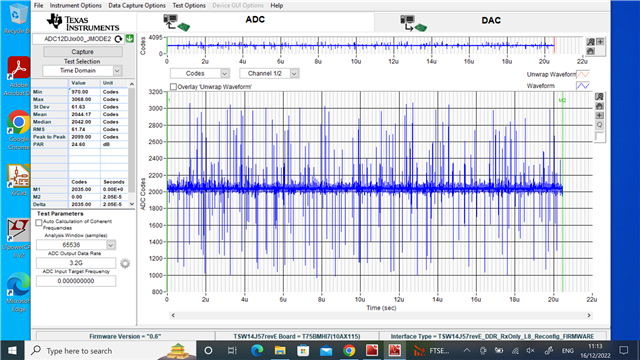

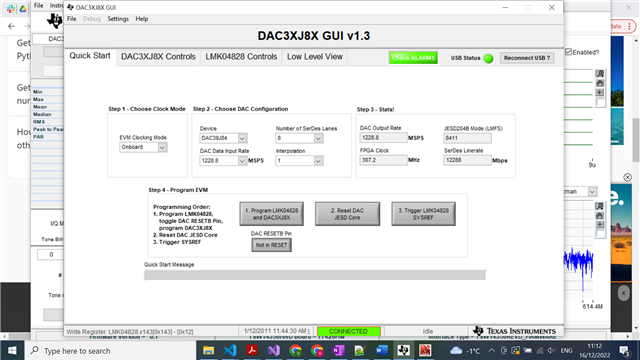

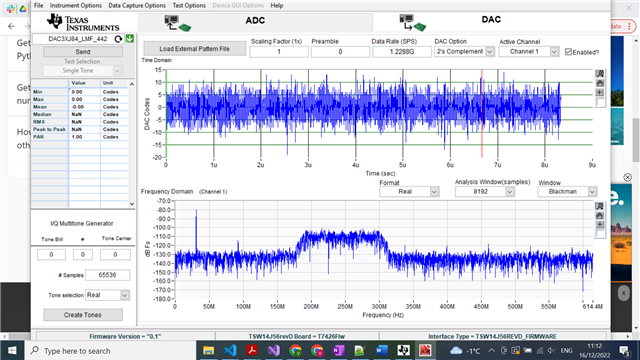

我们将发送一个模式(随附的屏幕截图),其峰值为25MHz,中心频率为200MHz 的宽带,如使用 DAC39J84EVM 和 DAC 设置的屏幕截图所示,如所附的图所示。 通过在 GUI 上加载外部图形文件(.csv 格式)将图形发送到 DAC、并附加该文件以供参考。 我们通过将 SMA 光纤直接从 DAC 连接到 ADC 的输入通道、将此模式直接发送到 ADC12DJ3200。 从 ADC 观察到的频谱和时域代码如下图所示。 输出时域的.csv 文件也已附加。 ADC 上的预期输出应该是 DAC 发出的模式、但两者之间存在明显差异。 我们在频谱分析仪和示波器上检查了 DAC 的输出、结果与 ADC 相同、这表明 DAC 的输出与发送的结果不同、并显示在 DAC GUI 上。 这是否有任何具体原因?

此外、关于 DAC 的采样率为2.8GSPS、但当通过 GUI 进入时、我们能够访问最大值为1228.8MSPS (DAC 数据输入速率)、我们如何访问 DAC 的完整采样率。 此外、是否有办法将 DAC 数据输入速率设为1GSPS 或某个整数值、因为这对我们的实验非常方便? 为此、我们需要做哪些更改、这是我们在 ADC 上获得此类结果的原因(DAC 无法以1GSPS 的速率进行采样)吗?

感谢您的考虑并期待您的回应。

e2e.ti.com/.../I-and-Q-signals-RRC-filter.csve2e.ti.com/.../Faulty_5F00_Pattern_5F00_Recieved.csv

e2e.ti.com/.../I-and-Q-signals-RRC-filter.csve2e.ti.com/.../Faulty_5F00_Pattern_5F00_Recieved.csv