大家好、我 将通过 SDATA 输入使用 ADS4125的待机功能、以便在数据采集之间节省一些功耗。 我确实观察到,通过结合使用 OE 和 STRANBY,我们可以节省更多的能源。

因此我在 FPGA OE =!STANDBY 中进行了编程。 遗憾 的是、当这两种器件一起使用时、稳定时间似乎很长、直到输出端出现有效数据。 我在数据表中找不到它、您能告诉我最大值吗? 当待机 模式始终处于低电平且仅应用 OE 时、不会出现此问题

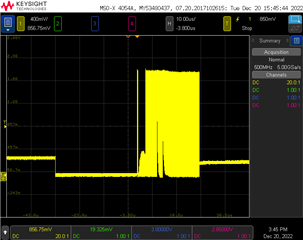

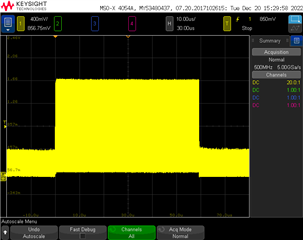

示例:

针对 OE 的 CLKOUT =始终高电平:

针对 OE 的 CLKOUT =!STANDBY: