我已将 DAC 子电路和电源序列发生器的原理图作为.docx 格式提供。 希望它们可读。

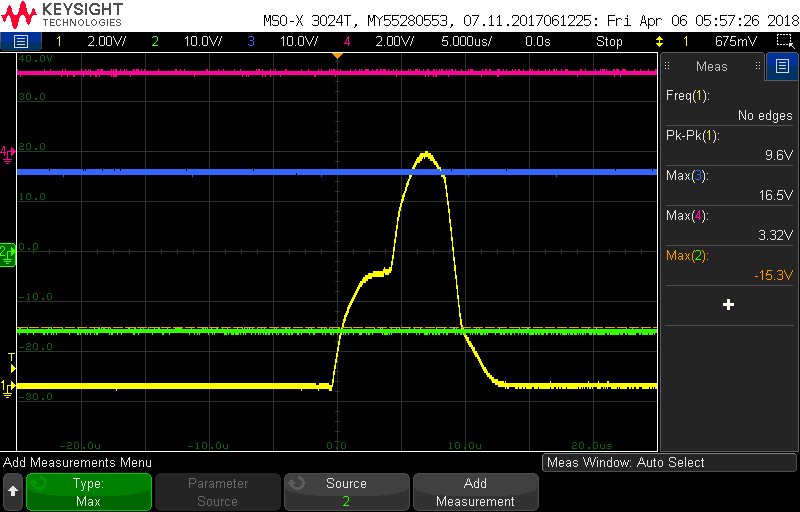

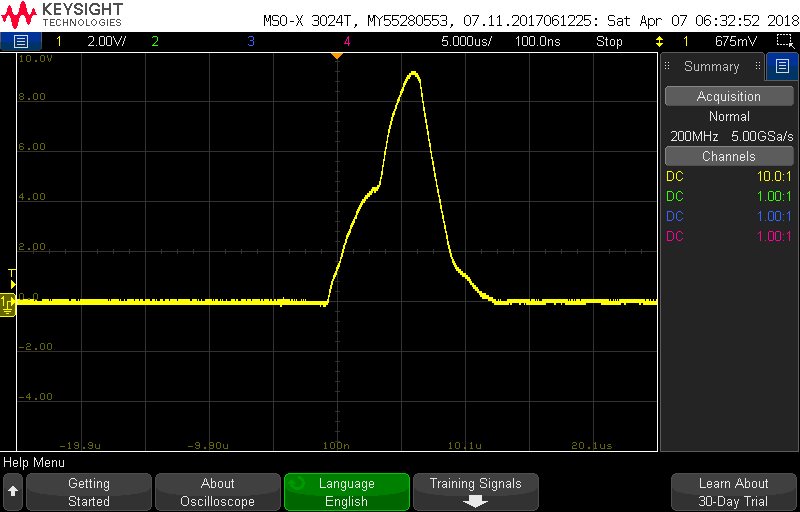

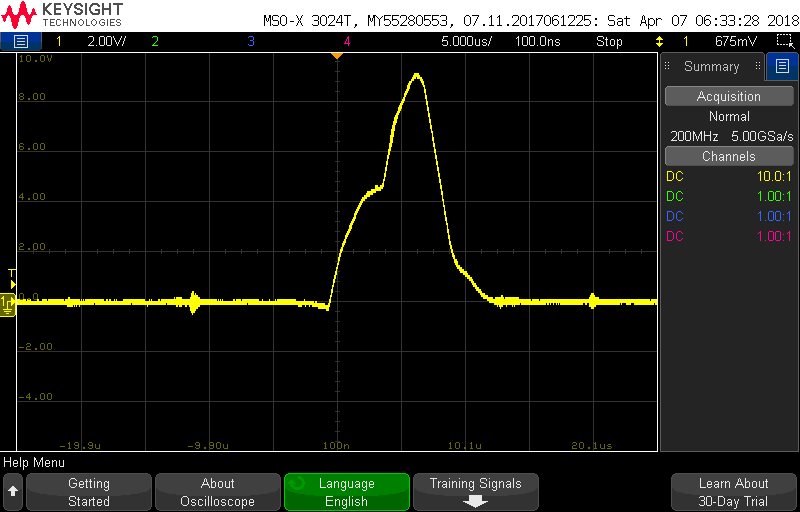

现在讨论这个问题。 我们以双极模式(+/-16.5V)运行 DAC8718、并将 RSTSEL 设置为 IOVdd、并将#USB 连接到 GND。 由于 REFA 和 B 上的基准电压为4.096V (它实际上是一个未连接到任何其他器件的基准电压)、我们可以看到启动时 DAC 输出上的电压为12.288V。 如果我们将 CLR 接地、它会将输出拉至0V、但 RST 或 LDAC 周期会将其恢复至12.288V。 如果我们引导器件并读取偏移寄存器、它们是0x0000。 如果我们向它们写入0x999A、则输出上的电压变为0V、我们可以从寄存器中读取我们写入的相同值(这似乎表明芯片认为我们也处于双极模式)。

为什么在启动时芯片的输出行为不是数据表所显示的那样(0x999A 被自动加载)。 这是个问题、因为我们的下游器件无法承受12+V 电源。

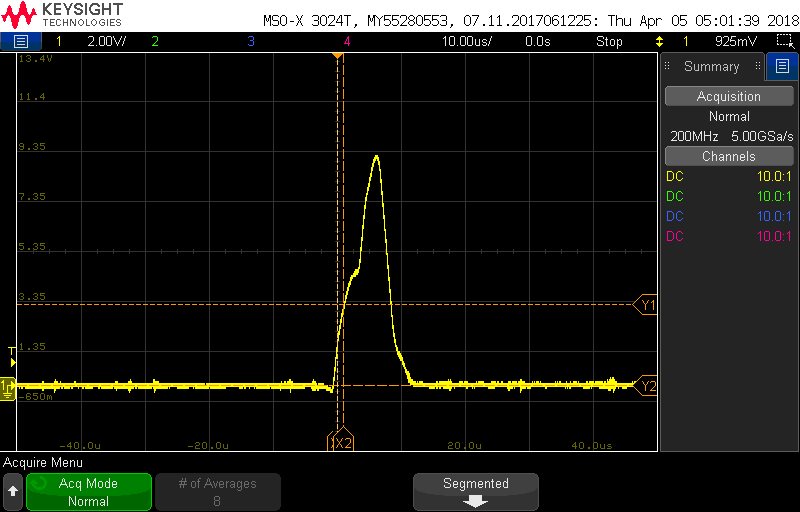

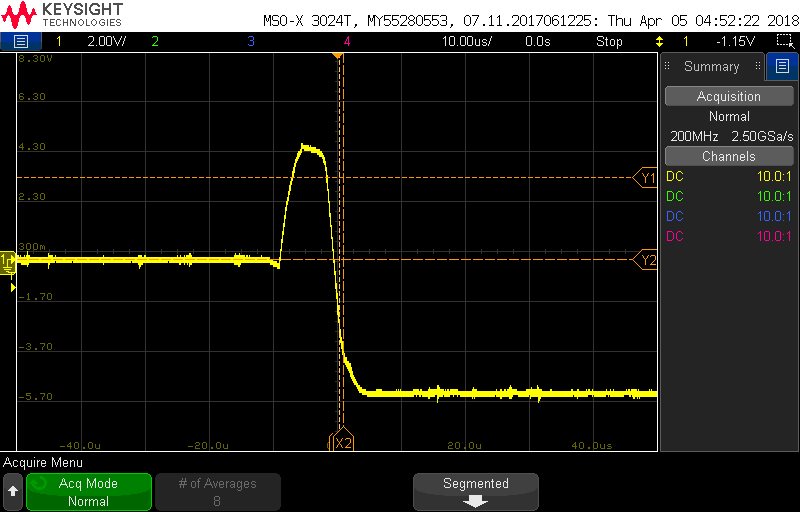

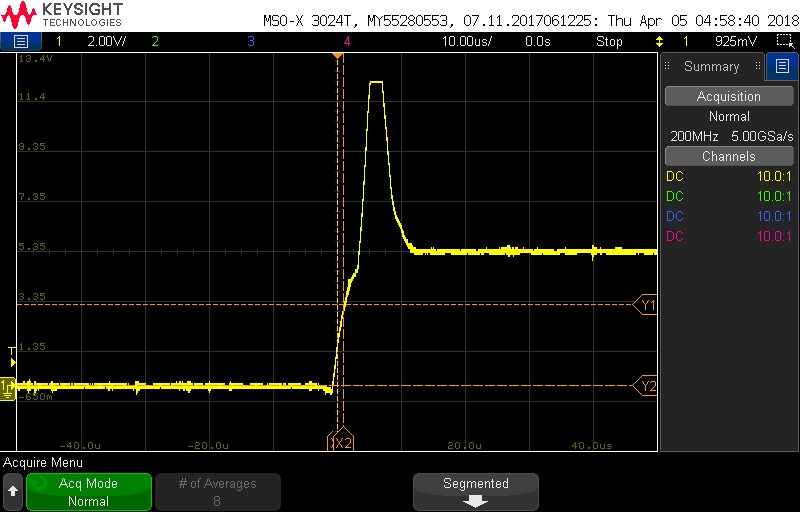

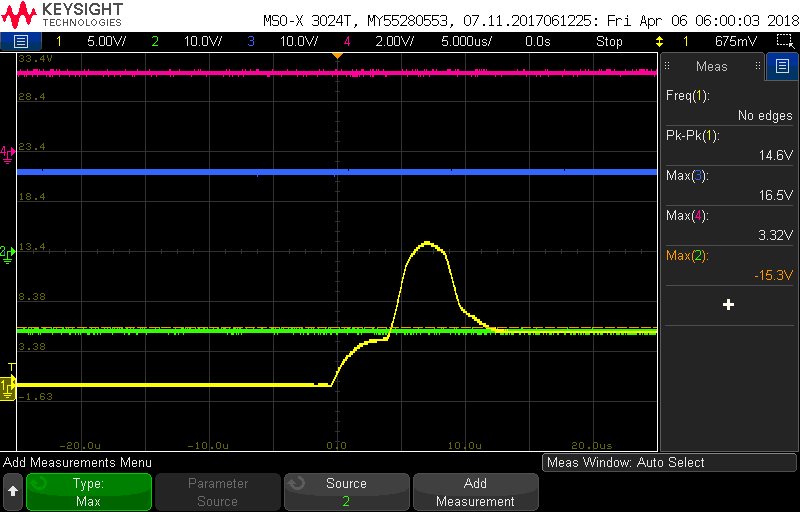

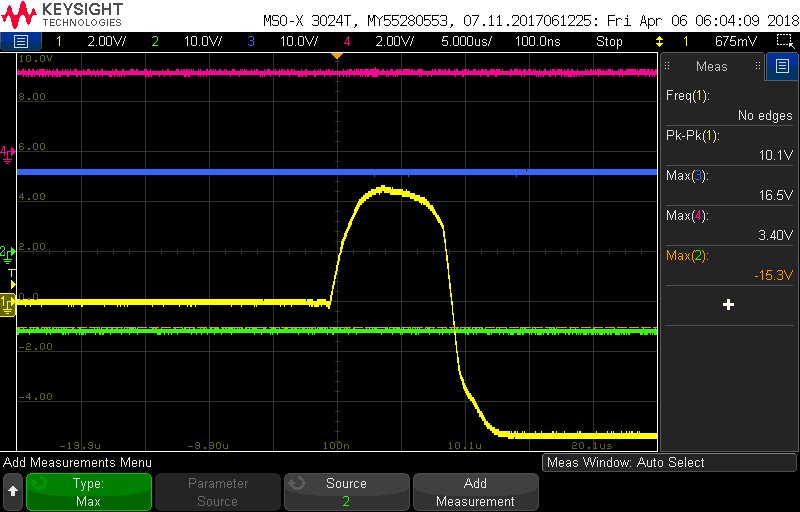

我们的电源也由 LM3880MF-1AA 芯片明确定序。 在 FLAP-A1 (IOVdd)上使用3V3 (2)、FLAP-A2 (DVdd)上使用5V (2)、FLAP-A3 (AVdd)上使用16V5、FLAP-A4 (AVss)上使用-16V5、在 FLAP-A5 (REF)上使用我们的基准。

我已将 EVM 连接到工作台电源、其中电源上的 IOVdd=DVdd=5V、电源上的 AVdd =16.5V、 在电源上 AVss =-16.5V、并使用板载5V 基准、同时导通5V 序列-> 16.5V ->-16.5V、并且行为相同。

有什么建议吗?