主题中讨论的其他器件: DAC38RF82、 ADC12J4000EVM

大家好、

我正在尝试将 DAC38RF82EVM 与 FPGA 板相连。 我已经完成了一个使用采样率为9GSPS 的单路(8位) DAC 的项目。

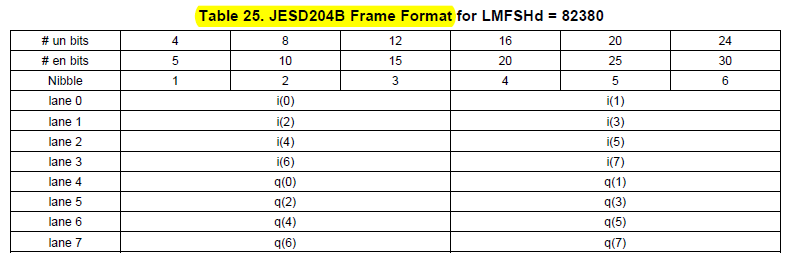

现在、我要将 DAC 配置为在双(12位) DAC 模式下运行。 我检查了 DAC38RF82的数据表、找到了如下表:

根据我的理解、i 对应 DAC A、q 对应 DAC B、每个都有12位。

但是、Vivado 的 JESD204B 内核仅接受每个 JESD 通道中的32位输入、不可达12位。 有人能告诉我们如何在 JESD 帧中排列数据吗?

我还注意到、如果我将 DAC 设置为在3GPS、双通道模式和12位分辨率下运行、则 JESD 串行通道速率为11250MHz。 这是否意味着 JESD 内核时钟为11250MHz/40 = 281.25MHz? 如果事实如此、则每个 DAC 将在 FPGA 时钟周期内收到3000/281.25 = 10.6667个样本、而不是整数。 我的理解是否有任何错误?

谢谢你。