主题中讨论的其他器件: ADS52J90、 LMK04826

你好

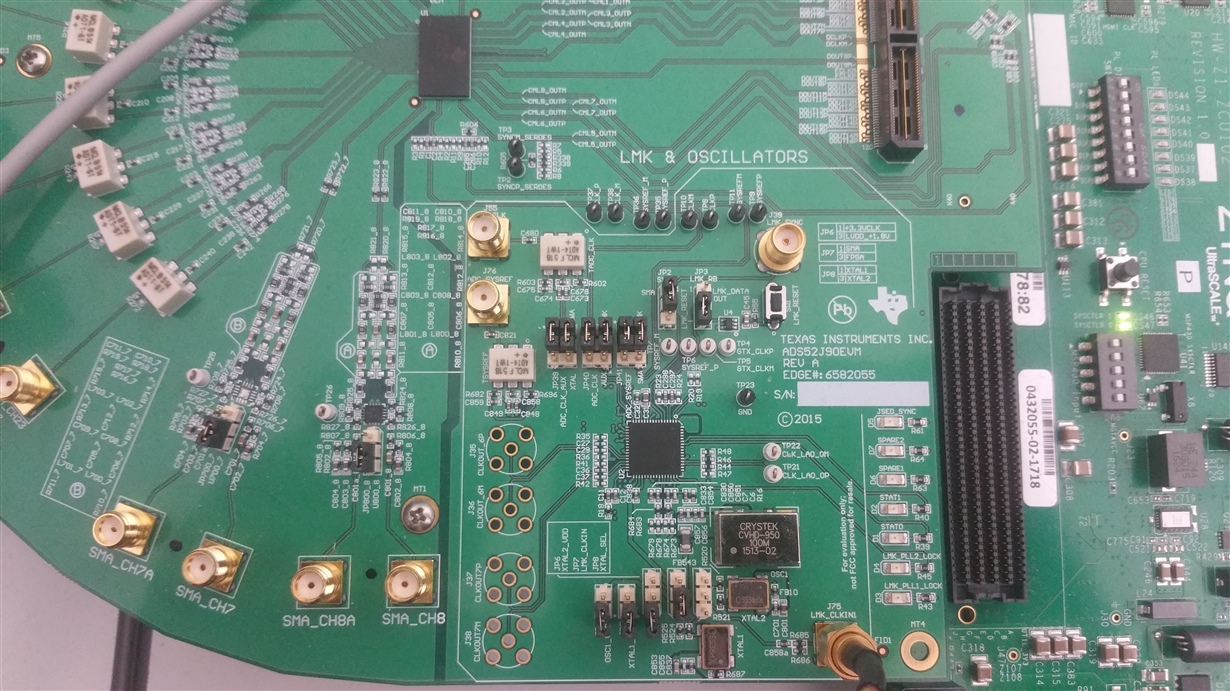

我正在使用 TI 的高速 ADC 板 ADS52J90EVM。 我使用 Xilinx Zynq UltraScale+板来读取 ADC 样本、但在此之前、我想查看 ADC 是否配置正确并提供了所有必需的信号。 因此、我已将 ILA 调试内核连接到 ADC 的端口。

我可以看到 Sysref 信号周期性地重复、Ref Clk 也在工作。 但 FPGA CLK 信号始终处于低电平。

我使用的是快速入门 JESD 配置。 (请参阅随附的文件)

请问问题是什么?

非常感谢您的帮助。

此致

Rizwane2e.ti.com/.../ADS52J90_5F00_16ch_5F00_SINE_5F00_4L_5F00_12x_5F00_12b_5F00_GBLCLKDIV1_5F00_FSDIV3_5F00_SYSREFDIV24_5F00_20x.cfg