主题中讨论的其他器件:ADS1282

吴约瑟;

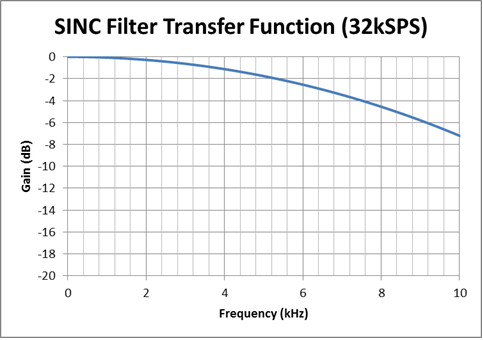

我尝试了解 FPGA 的数据速率。 第5页的最小 SCLK 周期为2* 2.50E-07 = 5E-07。 基本上是时钟速率的一半。 因此,我可以传输31位字的 fasted 为31*5E-07= 15.5e-06s。 如果最大 SINC 滤波器模式为128000SPS、即7.81E-6s 、则在 SINC 模式下、我向 FPGA 的最大传输速率实际上为64KSPS。 是这样吗? 在我可能不知道的模式下、最大传输速率是多少? 如果我旁路滤波器、采样率会上升吗?

对于我的应用而言、授予64KSPS 是一种完全终止功能、只是为了确保我了解数据速率并记录数据速率。

谢谢

Dean Gacita