您好!

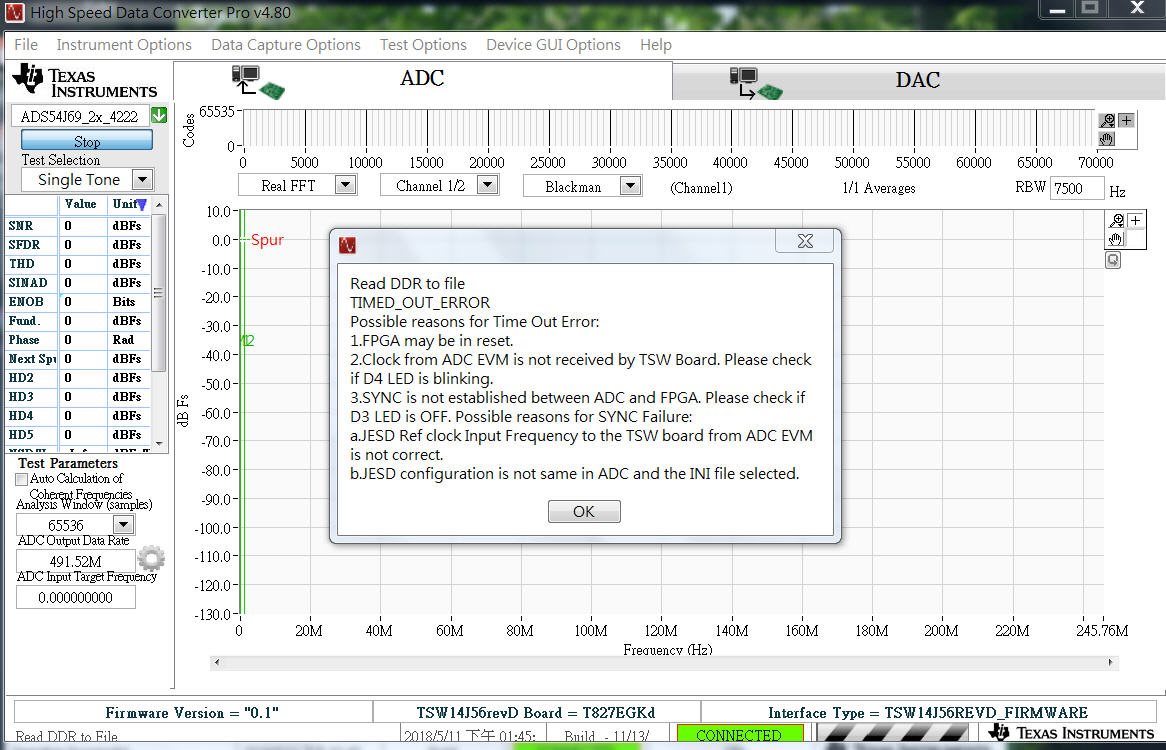

我在 HSDC 专业版软件中遇到有关"读取 DDR 到文件"的错误。 错误消息显示"Timed_Out_ERROR"。

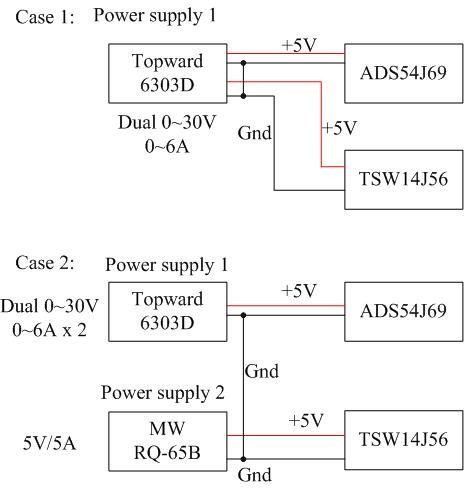

我的硬件是: ADC 板是 ads54j69 、 FPGA 板是 tsw14j56。

我的 HSDC 专业版设置为:

采样频率为491.52MHz、采样点为65536

函数发生器设置为10MHz、Ro=50 Ω、Amp =0.3vpp、bias =0.15v。

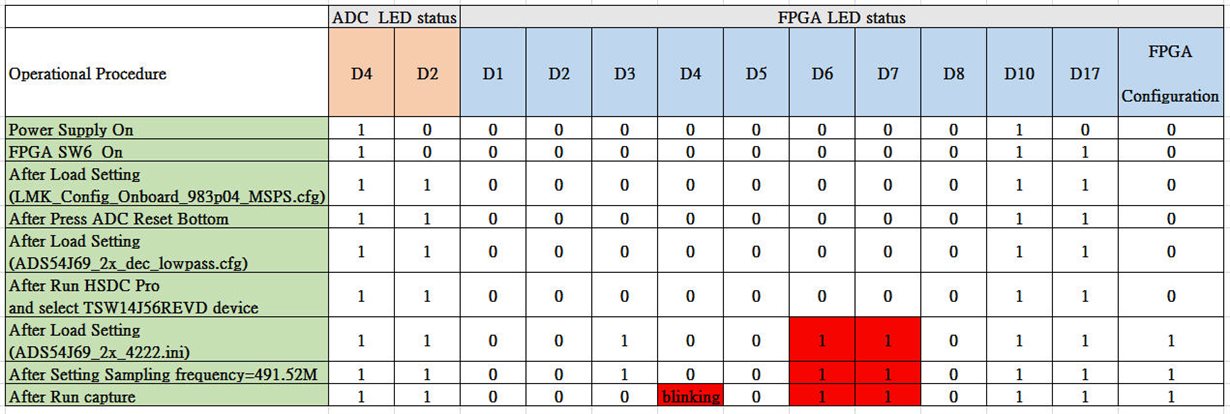

我已经检查了 FPGA 板中的 LED 状态、其中 D4 LED 闪烁、 D3 LED 熄灭。 和 ADC PLL2锁定(D2 LED 亮起)。

ADC 板的设置文件为 LMK_Config_Onboard _983p04_MSPS 和 ADS54J69_2x_dec_lowpass。

如何解决此超时错误? 这个问题使我感到困惑大约一周。

非常感谢您的帮助。