我在我们的设计中使用 DAC37J82。

DAC37J82与以下串行器/解串器配置一同使用:

LMFS 2221

K=16

Sysref:9.6Mhz

FS:614.4Mhz

内插:4.

通道速率:3072Mbps

153.6Mhz

外部时钟模式。

复数。

我们没有 EVM。

我们将使用 GUI 仿真。

我修改了电路板。

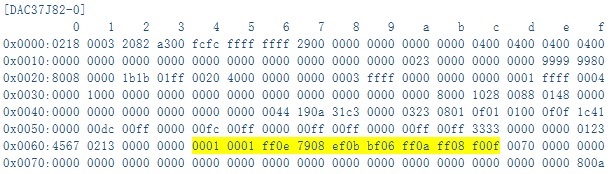

我设置 DAC37J82寄存器以进行 E2E 回复。

E2E 文件为"DAC37J82 FS 614.4 K 16.cfg"。

我们的问题如下。

JESD204B 链路未连接。

JESD204B PLL 不会锁定。

检查 JESD204B 的方法是什么?(寄存器检查?)

谢谢你