主题中讨论的其他器件: LM1085、 REF5025

您好!

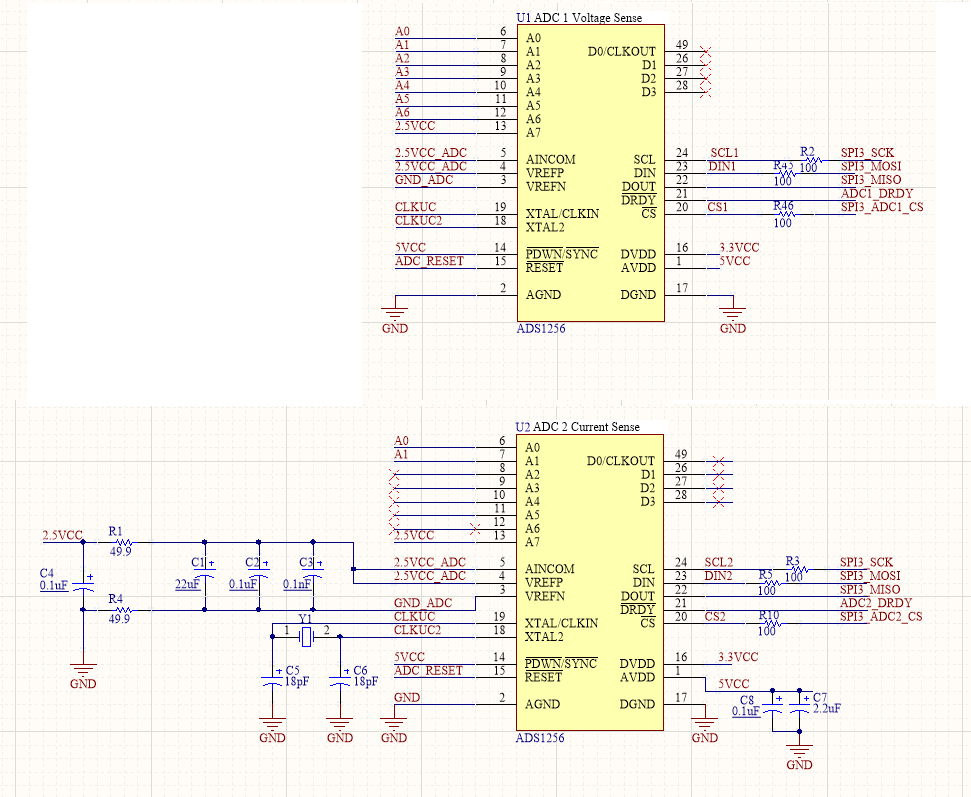

我目前正在设计一个使用两个并联 ADS1256芯片同时测量信号的设计。

下面列出了两个 ADC 同时读取的过程:

1.两个 ADC 的 WREG 通道到多路复用器稳压器

2.向两个 ADC 发送同步命令

3.向两个 ADC 发送唤醒命令

4、等待 ADC1的 DRDY 为低电平、然后向 ADC1发送 RDATA 命令

5、等待 ADC2的 DRDY 处于低电平、然后向 ADC2发送 RDATA 命令

在读取同一通道的每个过程之间、可能存在0.2mV 的读取尖峰。

就电路设置而言、ADC 共享同一个晶体(7.68MHz)。 。

两者之间共享 SPI 总线(芯片选择和数据就绪分离)。 AIN COM 和 VREFP 连接至2.5V、这也在两个 ADC 之间共享。

采样率:60SPS

输入缓冲器:关闭

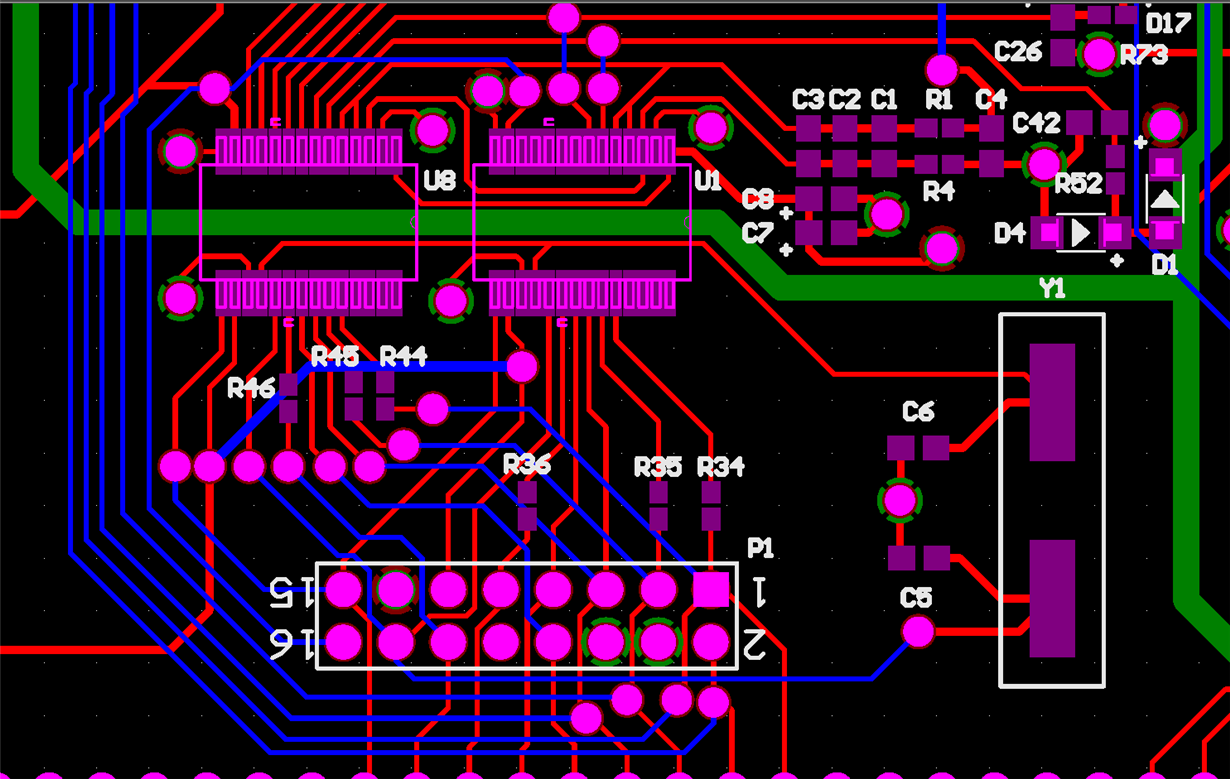

我确实在两个 ADC 的下方拆分了一个接地层、将数字侧和模拟侧分开、但它们在 PCB 的另一个部分重新连接在一起。 我想知道您能否提供一些建议、以便在运行两个并行 ADC 时更大限度地降低噪声、或者我可能错过了哪些特定的器件注意事项?

感谢您的观看、

Mike