相关人员、

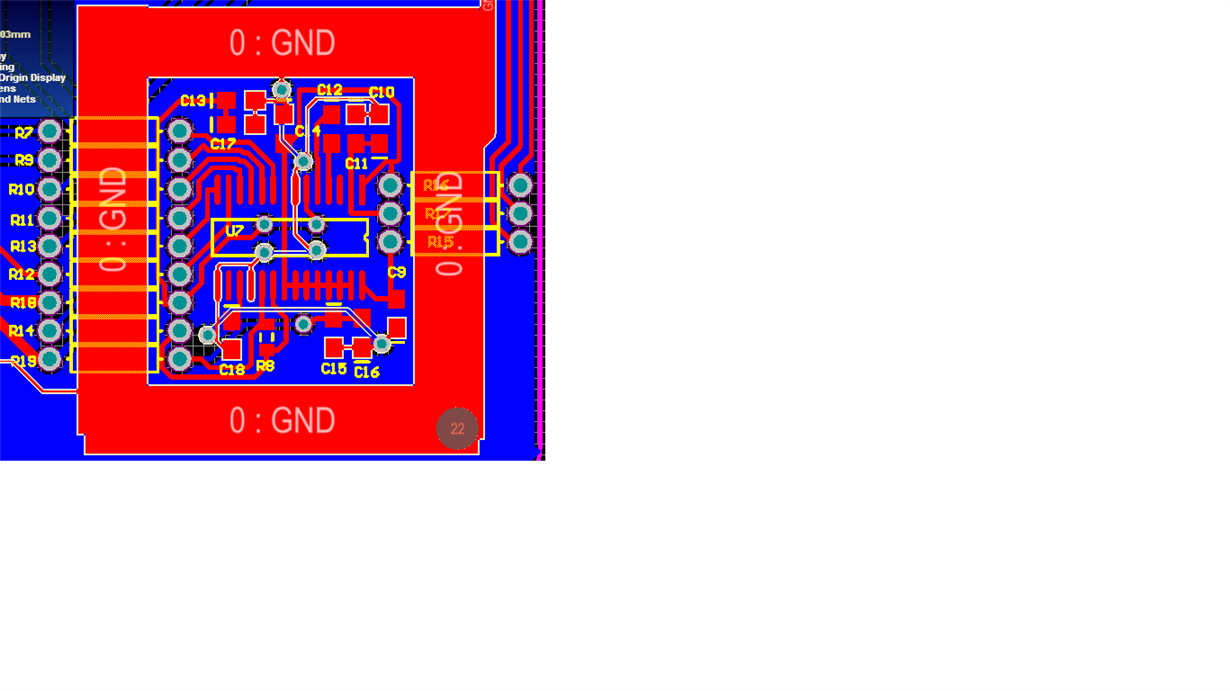

我叫 Celal。 我的电路包含在 ads1262、模拟陀螺仪(adxrs624)和 ESP8266 Arduino 板中。 附件中 ads1262的连接和 PCB 布局。 我使用此论坛中的通用代码、如下所示。

ADs1262_Reg_Write (power、0x11);delay (10);//11h (默认值)内部基准被启用

ADs1262_ReG_Write (interface、0x0D);delay (10);//05h (默认值)启用状态字节、启用校验和

ADs1262_ReG_Write (MODE0、0x00);delay (10);//00h (默认值)连续转换模式| 0x40脉冲转换模式(单次转换)

ADs1262_ReG_Write (MODE1、0x00);delay (10);//80h (默认值) FIR 滤波器| 00h sinc1 | 60h sinc4

ads1262_ReG_Write (Mode2、0x89);delay (10);//04h (默认值)启用 PGA 的1V/V 20sps| 5Ch 32V/V 7200sps | 5Fh 32V/V 38400sps

ADs1262_ReG_Write (INPMUX、0xEE);delay (10);//01h (默认值)多路复用器、AIN0 e AIN1 | 23h AIN2 e AIN3

ADs1262_Reg_Write (OFCAL0、0x00);Delay (10);//00h (默认值)偏移校准寄存器

ADs1262_Reg_Write (OFCAL1、0x00);Delay (10);//00h (默认值)偏移校准寄存器

ADs1262_Reg_Write (OFCAL2、0x00);Delay (10);//00h (默认值)偏移校准寄存器

ADs1262_Reg_Write (FSCAL0、0x00);Delay (10);//00h (默认值)满量程校准寄存器

ADs1262_Reg_Write (FSCAL1、0x00);Delay (10);//00h (默认值)满量程校准寄存器

ADs1262_Reg_Write (FSCAL2、0x40);Delay (10);//40h (默认值)满量程校准寄存器

ADs1262_ReG_Write (IDACMUX、0xBB);delay (10);//BBH (默认值)输出多路复用器、无连接、无连接

ads1262_ReG_Write (IDACMAG、0x00);delay (10);//00h (默认值)电流幅度、关闭

ADs1262_ReG_Write (REFMUX、0x00);Delay (10);//00h (默认值)基准多路复用器、2.5V、2.5V

ads1262_ReG_Write (TDACP、0x00);delay (10);//00h (默认值) TDACP、无连接

ADs1262_Reg_Write (TDACN、0x11);delay (10);//00h (默认值) TDACN、无连接

ADs1262_Reg_Write (GPIOCON、0x00);delay (10);//00h (默认值) GPIO 未连接

ADs1262_Reg_Write (GPIODIR、0x00);delay (10);//00h (默认值) GPIO 输出

ADs1262_Reg_Write (GPIODAT、0x00);delay (10);//00h (默认值) GPIO 低电平

ADs1262_Reg_Write (ADC2CFG、0x00);delay (10);//00h (默认值) ADC2

ADs1262_ReG_Write (ADC2MUX、0x01);delay (10);//01h (默认值)

ADs1262_ReG_Write (ADC2OFC0、0x00);delay (10);//00h (默认值)

ads1262_ReG_Write (ADC2OFC1、0x00);delay (10);//00h (默认值)

ADs1262_ReG_Write (ADC2FSC0、0x00);delay (10);//00h (默认值)

ADs1262_ReG_Write (ADC2FSC1、0x40);delay (10);//40h (默认值)

spi.transfer (start);

根据 数据表、我选择了正极和负极等模拟输入的测试 DAC、两者之间的差值约 为7.8125mV。 我得到的结果为7.84mV 至8.15mV。 simple span=(8.15-7.84)/(8.15+7.84)/2)*100=4%

我预期的 是简单量程的0.4%、 但 ADC 输出 的光度是预期的10倍。

您能否提出有关改进结果的任何提示或技巧?