请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC37J84EVM 主题中讨论的其他器件:LMK04828

大家好、

我的客户在用户指南的设置过程中使用了 DA37J84EVM。

确认 EVM 正常运行后、在 JESD 块选项卡中将 K 值从初始值10更改为22。

然后他们单击了2。 "Reset DAC JESD Core (重置 DAC JESD 内核)"按钮、然后单击3。 触发 LMK04828 SYSREF 按钮。

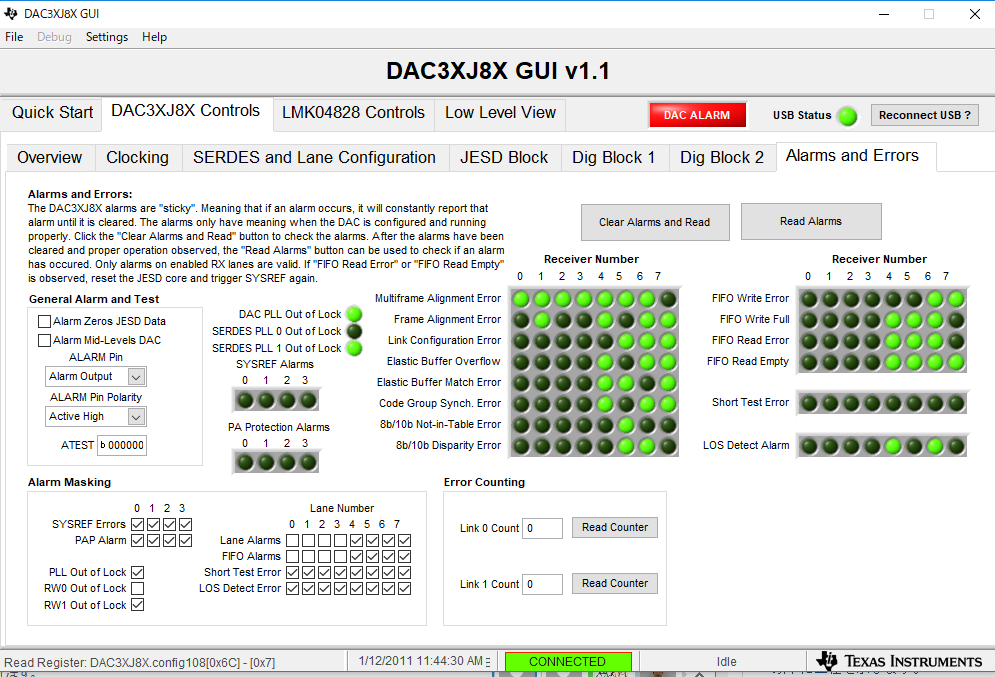

但 EVM 报告 了多帧对齐错误和帧对齐错误。

更改 K 值的设置过程是什么?

此致、

Toshi