Thread 中讨论的其他器件: TMS320C203

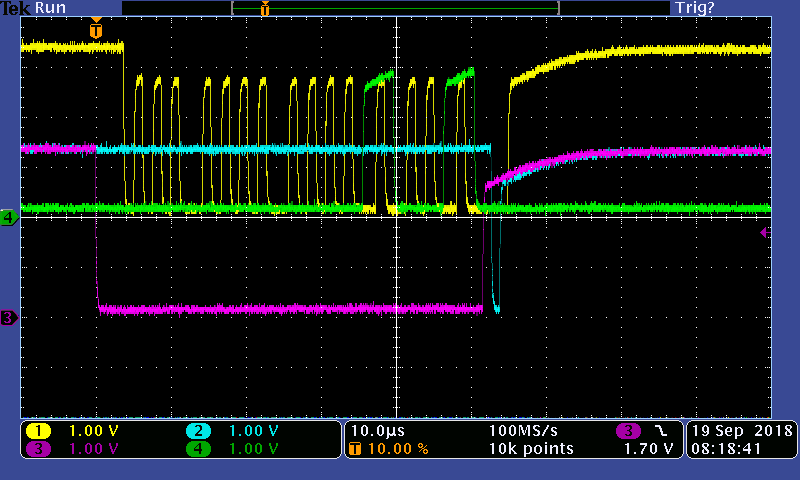

TLV5614的修订版 B 数据表并未满足 LDAC*引脚的时序要求。 能否提供一些见解?

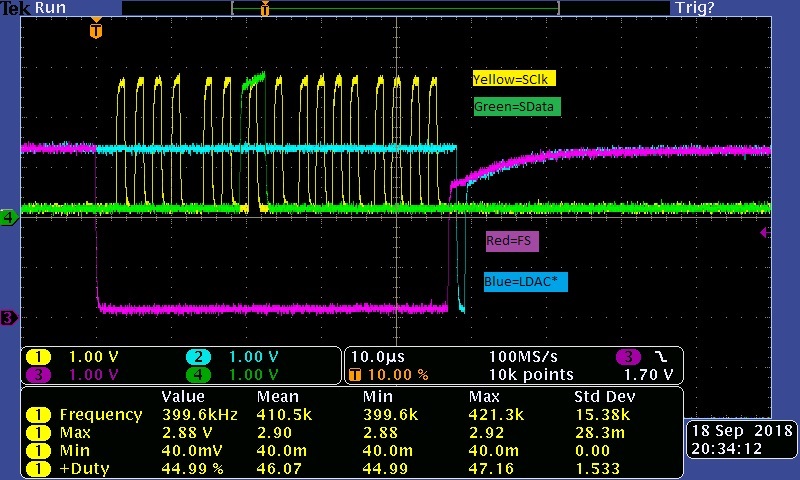

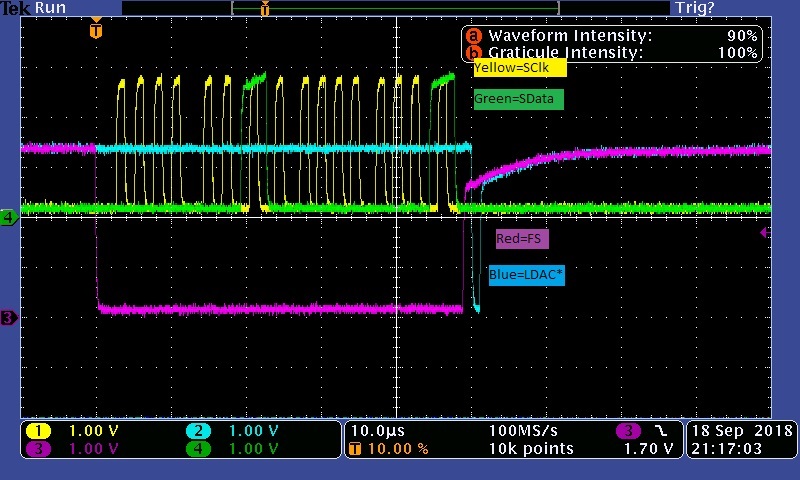

背景 我在 持续更新输出方面遇到问题。 似乎每隔一段时间更新一次。

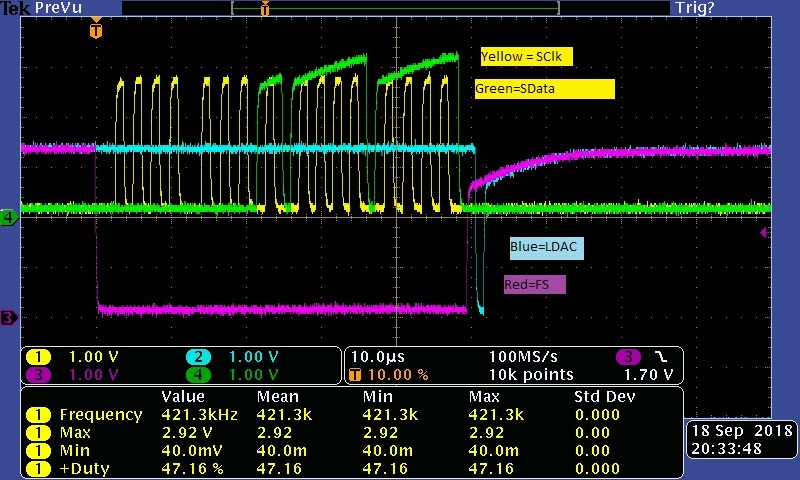

我按照数据表的时序要求加载寄存器、这些要求是:

CS*低电平,然后 FS 低电平。 然后在 CS*和 FS 均为低电平时加载16位。 然后、FS 为高。

之后(更新 输入寄存器), 将 LDAC*拉低。 延迟(在对 LDAC* lo 进行脉冲之前在 fs hi 之后) =~1us,在返回 LDAC* HI 之前 LDAC*处于低电平~1us。

有什么规格或建议?