链中的第二个器件也存在此问题。 以下是这些行动的记录。

在复位线路的硬件置为有效后、我正在执行的初始化例程开始。

我已将回复配对、以快速反映命令与命令状态响应。

我正在使用 MSP432连接 ADS131A04。 第一个器件处于异步中断模式、第二个器件是同步从器件。

我的问题可能是由于 CMD_NULL 被发送、而第二个器件的应答表明重新同步故障。

重新同步故障。

每当信号路径因而暂时复位时、该位就会被置位

DRDY 同步事件。 该故障只能在同步模式下发生

从机模式。

0:设备处于同步状态

1:信号路径瞬间复位以保持同步

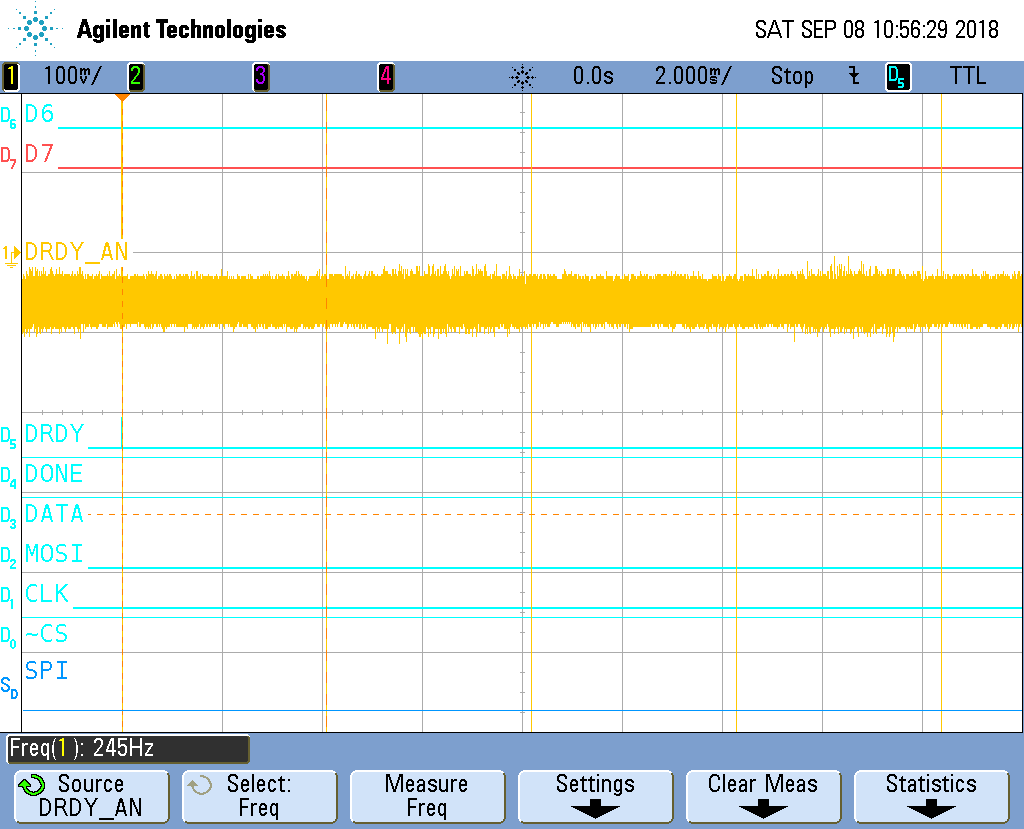

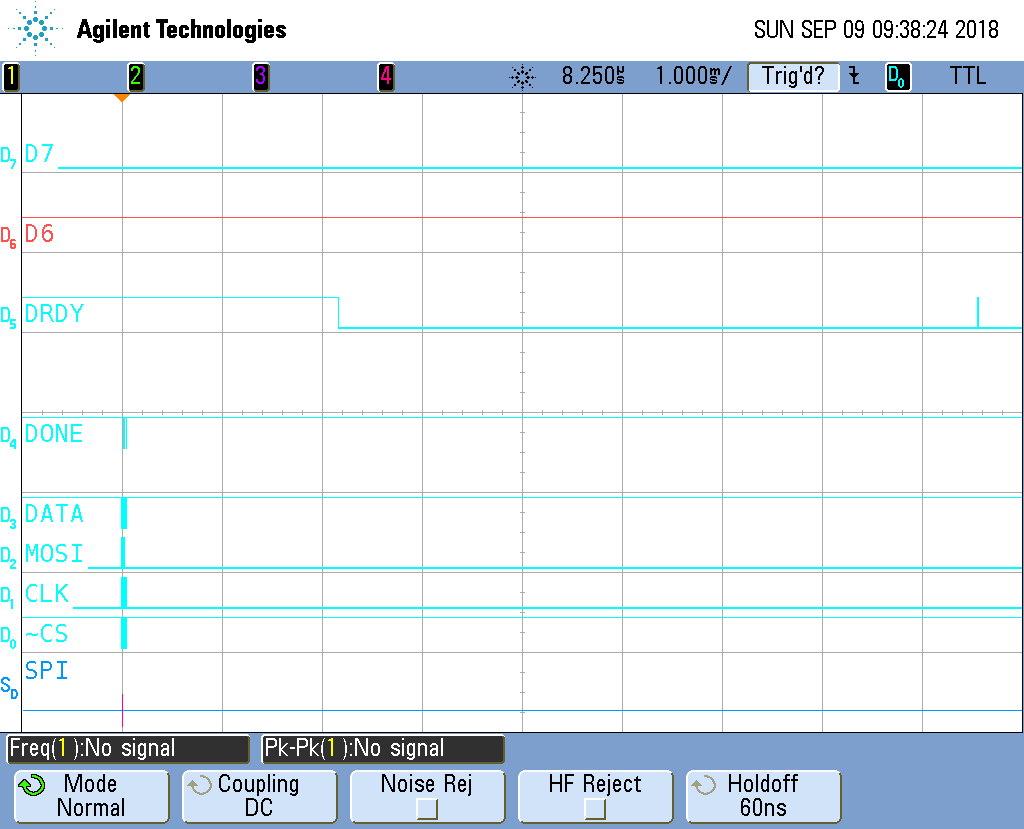

我正在使用下降沿 DRDY 输入信号在示波器上触发...并且不观察任何毛刺脉冲。

但是、我发现即使在发送 STANDBY 命令之后、DRDY 中断也会以编程的数据速率传入。

活动状态是一个高边沿到低边沿的转换、但是、随着我的菜单化、信号线会以编程的数据速率自行复位(在 ADS131A04传送新边沿之前返回高电平。

在 ADS131A04.pdf (SBAS590D)第50页的手册中提到了对 ADCx 寄存器的写入。

不过、这些寄存器用于数字增益、因此我假设 ADC_ENA 是预期禁用寄存器。

我不确定如何继续、因此我忽略了 Resynch_FAULT 和继续配置。

在尝试写入第二个器件中的 ADC_ENA 寄存器之前、所有值都显示良好。

从那一刻起,我就无法解释发生了什么。

下面是我之前描述的与2个 ADC 的通信序列。

我包含了与器件的十六进制字状态响应直接配对的(十六进制命令字/命令字类型)。

j3:Cmd 已解析:found (initADC){}

就绪状态 0x82->DEV1回复

0x7f82 --> DEV2回复

CMD_RESET 0x04 --> DEV1应答

0x04 --> DEV2回复

CMD_UNLOCK 0x0655 --> DEV1应答

0x0655 --> DEV2回复

CMD_STANDBY 0x0022 --> DEV1应答

0x0022--> DEV2回复

CMD_NULL 0x2200 --> DEV1应答

0x2204 --> DEV2回复

CMD_UNLOCK 0x0655 --> DEV1应答

0x0655 --> DEV2回复

CMD_RREG|ID_MSB 0x2004 --> DEV1回复

0x2004 --> DEV2回复

CMD_RREG|ID_LSB 0x2103->DEV1应答

0x2103->DEV2应答

CMD_RREG|STAT_1 0x2200 --> DEV1应答

0x2200 --> DEV2回复

CMD_RREG|STAT_P 0x2300 --> DEV1应答

0x2300 --> DEV2应答

CMD_RREG|STAT_N 0x2400 --> DEV1应答

0x2400 --> DEV2回复

CMD_RREG|STAT_S 0x2500 --> DEV1应答

0x2500 -->DEV2应答

CMD_RREG|STAT_M2 0x2709 --> DEV1应答

0x270a --> DEV2回复

CMD_RREG|A_SYS_CFG 0x2b60 --> DEV1应答

0x2b60 --> DEV2回复

CMD_RREG|D_SYS_CFG 0x2c3c --> DEV1应答

0x2c3c --> DEV2回复

CMD_RREG|CLK1 0x2d08 --> DEV1应答

0x2d08 --> DEV2回复

CMD_RREG|CLK2 0x2e86 --> DEV1应答

0x2e86 --> DEV2应答

CMD_RREG|ADC_ENA 0x2f00 --> DEV1应答

0x2f00 --> DEV2应答

CMD_RREG|ADC1 0x3100 --> DEV1应答

0x3100 --> DEV2应答

CMD_RREG|ADC2 0x3200 --> DEV1应答

0x3200 --> DEV2回复

CMD_RREG|ADC3 0x3300 --> DEV1应答

0x3300 --> DEV2应答

CMD_RREG|ADC4 0x3400 --> DEV1应答

0x3400 --> DEV2回复

WREG=0x4d00 0x2d00 --> DEV1应答

0x2d00 --> DEV2应答

WREG=0x4e00 0x2e00 --> DEV1应答

0x2e00--> DEV2应答

CMD_RREG|CLK1 0x2d00 --> DEV1应答

0x2d00 --> DEV2应答

CMD_RREG|CLK2 0x2e00 --> DEV1应答

0x2e00--> DEV2应答

WREG=0x4f0f 0x2f0f --> DEV1应答

0x0000 --> DEV2应答

CMD_RREG|ADC_ENA 0x2f0f --> DEV1应答

0x0000 --> DEV2应答

CMD_WAKEUP 0x0033 --> DEV1应答

0x0000 --> DEV2应答

CMD_LOCK 0x0555 --> DEV1应答

0x00cb --> DEV2回复

我似乎需要解决第二个器件上的 Resynch_FAULT 问题、但我无法决定如何解决该问题。

谢谢你们的帮助!!!