Other Parts Discussed in Thread: ADS131A04, OPA1678, ADS131A04EVM

主题中讨论的其他器件: OPA1678、

请告诉我以下有关 ADS131A04设置的三点。

①Negative 电荷泵输出(NVCP)

如果未使用 VNCP、则 VNCP 是否确实连接 AVSS、对吧?

EVM 用户手册 P16介绍了设置完成后应连接 JP8。

这种情况是否仅适用于使用 NVCP?

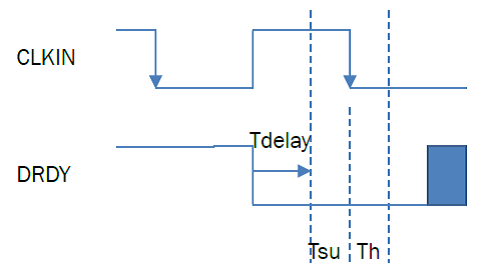

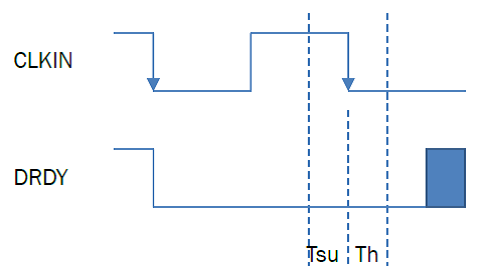

针对/DRDY 和时钟(CLKIN 或 SCLK)的 μ ②时序

请告诉我有关/DRDY 和时钟的建议时序。

客户担心亚稳态、

・这种情况是由 CLKIN 上升引起的/DRDY、但 Tdelay 的裕度很小。

・这种情况是由 CLKIN 下降引起的/DRDY、但我认为可能发生转移。

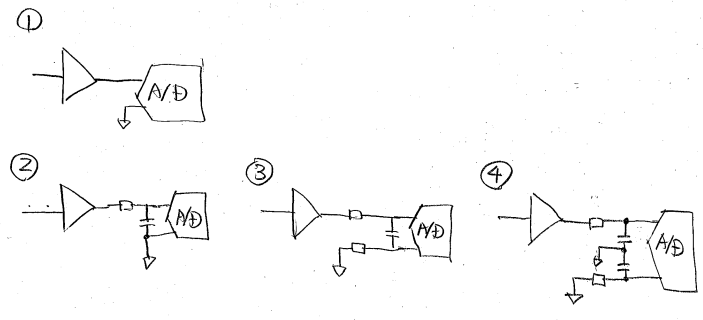

③Input 连接

如果 ADS131A04输入侧(AINx)连接 OPA1678、是否需要 RC 滤波器来连接 OPA1678输出和 ADS131A04输入?

还是直接连接没有问题?

此致、

Satoshi