主题中讨论的其他器件: LMK04828

- 条件

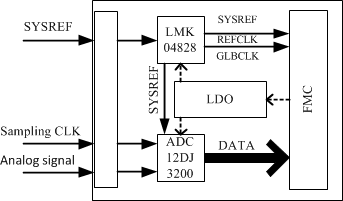

一个 XC7VX690T 承载两个 ADC12DJ3200 FPGA 夹层卡。 FMC 的结构如下。

LMK04828配置为0延迟模式、并提供 SYSREF、REFCLK 和 GLBCLK。

LMK04828首先通过 SPI 配置、然后通过 SPI 配置 ADC。

ADC 使用 JMODE0。

- 现象

当使用 JESD204B 测试模式控制寄存器(地址= 0x205)= 4:斜坡测试模式时、两个 ADC 采集同步、也就是说、每次上电时、来自两个 ADC 的数据可以对齐(在 MATLAB 中绘制波形)。

其他条件保持不变。 当只将 JESD204B 测试图形控制寄存器(地址= 0x205)更改为0:正常运行时、模拟信号由信号源的分压器分压提供正弦波。 在 MATLAB 中绘制波形。 在一种配置条件下、起始点的相对关系不会随每次触发而变化。 但未对齐。 通过 SPI 重新配置 ADC、所采集数据的起始位置将发生变化。

- 问题

1、在斜坡测试模式下、两个 ADC 同步、在正常运行模式下、采集的数据不对齐。 这表示 JESD204B 链路同步和 ADC 内核采集未同步。 是这样吗?

2、同步两个 ADC 时、是否有任何特殊的 ADC 初始化时序? 例如、复位 ADC 内核。

3、SPI 时钟是否有特殊要求?

4、还有什么可以做的呢?

提前感谢您的回答。