大家好!

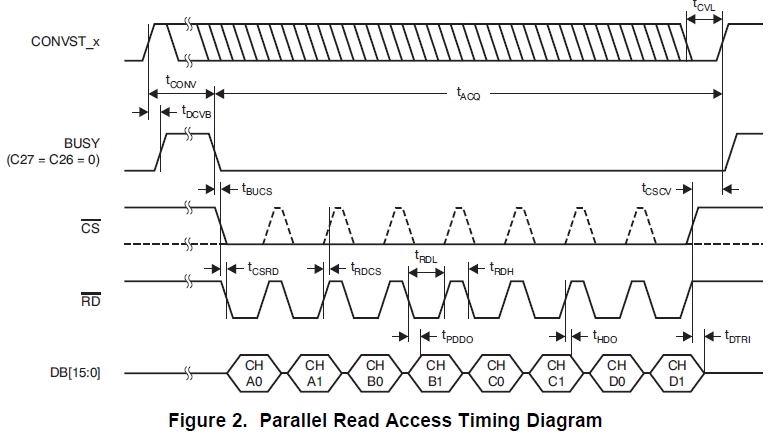

我有一个配置为硬件模式的 ADS8568定制板。 我使用微控制器生成的 PWM 触发覆盖;所有4个 CONVST 引脚接收相同的信号。

在我的固件中、我检查两个连续的繁忙 下降沿之间的延迟、我注意到有时延迟远低于 PWM 周期。

通过使用示波器分析问题、我注意到存在与任何 CONVST 无关的杂散 BUSY 信号(CONVST 很干净且陡峭、因此不是由该信号上的噪声引起的)。 调试这个问题、我注意到这些"尖峰"的频率与读取频率有关。 例如、读取所有4个通道时、我将每10秒出现一次杂散繁忙。 如果我在繁忙的下降沿之后没有读取任何内容、我将不会得到虚假的繁忙。

为了进行测试、我使用的是慢 CONVST (50Hz)。 如前所述、ADS8568处于 HW 模式、并行接口。

有什么想法吗?

谢谢