主题中讨论的其他器件: ISO7240M

当电源打开时、有一段时间 RC 引脚处于低电平。

上电后、BUSY 信号保持低电平、不会返回高电平。 如何使 ADC 返回正常模式。

此致、

西泽

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

ADS8509上的 R/C 引脚是一个数字输入引脚、这意味着主机器件正在对其进行控制。 这不是器件的输出、因此、如果 RC 信号不满意、主机器件(微控制器或类似器件)是问题的根源、这就是问题所在。

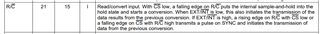

如下面的引脚说明状态所示、引脚的状态可以启动一个转换、从而导致 BUSY 处于活动状态、器件似乎按预期响应。

我建议在启动期间、主机器件将 RC 引脚保持在高电平、直到系统完全通电并稳定。 主机可以从此处开始与器件通信并开始转换。

如果您想共享原理图、我们可以对其进行审阅。

此致

Cynthia

你好、Cynthia

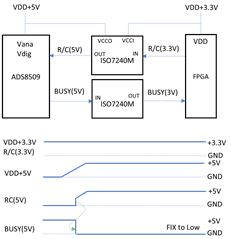

原理图和时序图如下所示。

VDD+3.3V 处的电压稳定。

然后、当 VDD+5V 电源打开时、提供给 ADS8509 的 VDD+5V 逐渐增加、但当电源由于 ISO7240M 而变为2.5V 时、R/C 信号上升至 VDD+5V。

这会导致 ADS8509输出 BUSY 信号。

问题是、该 BUSY 信号保持低电平、永远不会恢复到高电平。

在数据表中、tw2最大为2.2us、但 BUSY 信号永远不会恢复为高电平。

如何从外部复位 ADS8509?

此致

西泽

您能否澄清一下、在器件上电之前 RC 引脚是否高达3.3V? 如果是、这违反了绝对最大值、则任何数字引脚都不应大于器件的 Vdig。 虽然这可能不会由于处于此状态的时间较短而对器件造成损坏、但我建议解决此问题。

该器件没有要求严格的上电序列、但我怀疑在上升过程中会出现意外行为。 在此期间、您能否观察器件上的其他引脚、尤其是 CS。

您是否尝试过 PWRD 引脚、这将使模拟电路断电。

此致

Cynthia

您好!

您是否有机会推进这项工作?

我建议在启动器件时使 RC 处于高电平状态、而不是像现在那样处于低电平状态。 这可以通过上拉电阻器来完成、或更改主机器件内的状态。 该器件当前以低电平状态启动 CS 和 RC、这将启动转换、甚至在 ADC 完全通电并稳定之前也是如此。

CS 和 PWRD 均硬接地、因此与器件进行通信以开始转换的唯一方法是通过 RC

此致

Cynthia