Other Parts Discussed in Thread: ADS7223

大家好、团队、

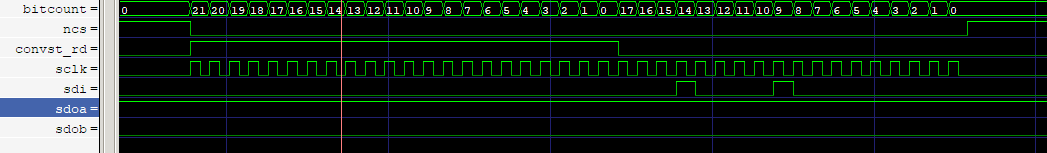

我确实有关于 ADS7223接口的问题。 它将连接到 FPGA。 ADC 将以伪差动配置运行、并且将启用全时钟模式。 附加 了计划时序的仿真。 我们需要组合 CONVST 和 RD 信号。 在附加的示例中、出于目的、SDO 和 SDA 被驱动为1或0。 需要注意的是、时序中尚未显示的 是 CONVST_RD 波形的12ns 或 SCLK 的第一个边沿。 这将得到实施。

根据数据表、我们的理解是、当结合使用 CONVST_RD 时、在将 CONVST_RD 切换为1时、NCS 必须设置为0。 这种理解是否正确? 我们找不到 NCS->0到 CONVST_RD->1之间的时序限制。 在我们的示例中、我们同时进行了两次转换。 是否存在时序限制?

此外,CONVST_RD->0读取数据的时序是否正确,或者是否必须在更早的时候发生一半或全部 SCLK? 在位数为17的示例中、我们希望 已经报告 MSB 或 ADC 通道。

非常感谢

Lutz