主题中讨论的其他器件: ADC12J4000EVM

大家好、

我使用 DAC38RF82EVM 连接 Virtex 7 FPGA 板。

DAC×在双 DAC (16位)模式下工作、具有3.2GSPS、2k Ω 内插。 我在 DAC38RF82EVM GUI 中成功完成了之前的设计、但没有收到任何警报。

但是、在我在这个项目中加入了一个 ADC12J4000EVM 并完成了另外一个项目之后、出现了一些警报 DAC38RF82EVM GUI。 尽管 DAC 具有输出并且看起来是正确的、但我担心未来的设计可能会遇到不可预测的问题、因为存在一些警报。

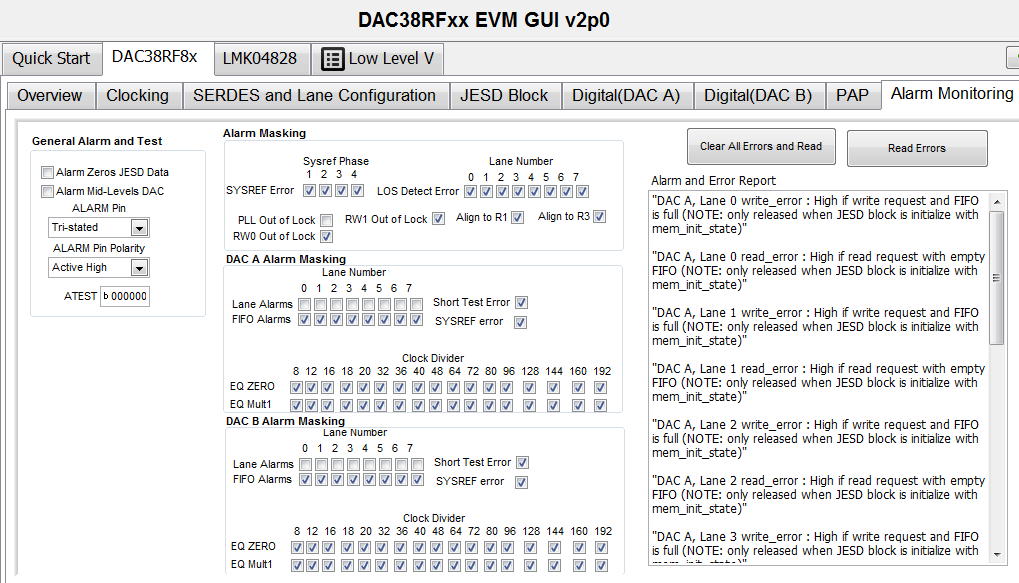

报警如下。

"

"DAC A、通道0 WRITE_ERROR:High if write request and FIFO is full (注意:仅当 JESD 块使用 mem_init_state 进行初始化时才释放)"

"DAC A、通道0 Read_error:High if read request with empty FIFO (DAC A、通道0 Read_error:High if read request with empty FIFO (注意:只有在 JESD 块使用 mem_init_state 初始化时才释放)"

"DAC A、通道1 WRITE_ERROR:High if write request and FIFO is full (注意:仅当 JESD 块使用 mem_init_state 进行初始化时才释放)"

"DAC A、通道1 Read_error:High if read request with empty FIFO (DAC A、通道1 Read_error:High if read request with empty FIFO (注意:只有在 JESD 块使用 mem_init_state 进行初始化时才会释放)"

"DAC A、通道2 WRITE_ERROR:High if write request and FIFO is full (注意:仅当 JESD 块使用 mem_init_state 进行初始化时才释放)"

"DAC A、通道2 Read_error:High if read request with empty FIFO (注:只有在 JESD 块使用 mem_init_state 初始化时才释放)"

"DAC A、通道3 WRITE_ERROR:High if write request and FIFO is full (注意:仅当 JESD 块使用 mem_init_state 进行初始化时才释放)"

"DAC A、通道3 Read_error:High if read request with empty FIFO (注意:只有在 JESD 块使用 mem_init_state 初始化时才释放)"

"DAC B、通道4 WRITE_ERROR:High if write request and FIFO is full (注意:仅当 JESD 块使用 mem_init_state 进行初始化时才释放)"

"DAC B、通道4 Read_error:High if read request with empty FIFO (注意:只有在 JESD 块使用 mem_init_state 初始化时才释放)"

"DAC B、通道5 WRITE_ERROR:High if write request and FIFO is full (注意:仅当 JESD 块使用 mem_init_state 进行初始化时才释放)"

"DAC B、通道5 Read_error:High if read request with empty FIFO (DAC B、通道5 Read_error:High if read request with empty FIFO (注意:只有在 JESD 块使用 mem_init_state 初始化时才释放)"

"DAC B、通道6 WRITE_ERROR:High if write request and FIFO is full (注意:仅当 JESD 块使用 mem_init_state 进行初始化时才释放)"

"DAC B、通道6 Read_error:High if read request with empty FIFO (DAC B、通道6 Read_error:High if read request with empty FIFO (注意:只有在 JESD 块使用 mem_init_state 初始化时才释放)"

"DAC B、通道7 WRITE_ERROR:High if write request and FIFO is full (注意:仅当 JESD 块使用 mem_init_state 进行初始化时才释放)"

"DAC B、通道7 Read_error:High if read request with empty FIFO (DAC B、通道7 Read_error:High if read request with empty FIFO (注意:只有在 JESD 块使用 mem_init_state 初始化时才释放)"

"

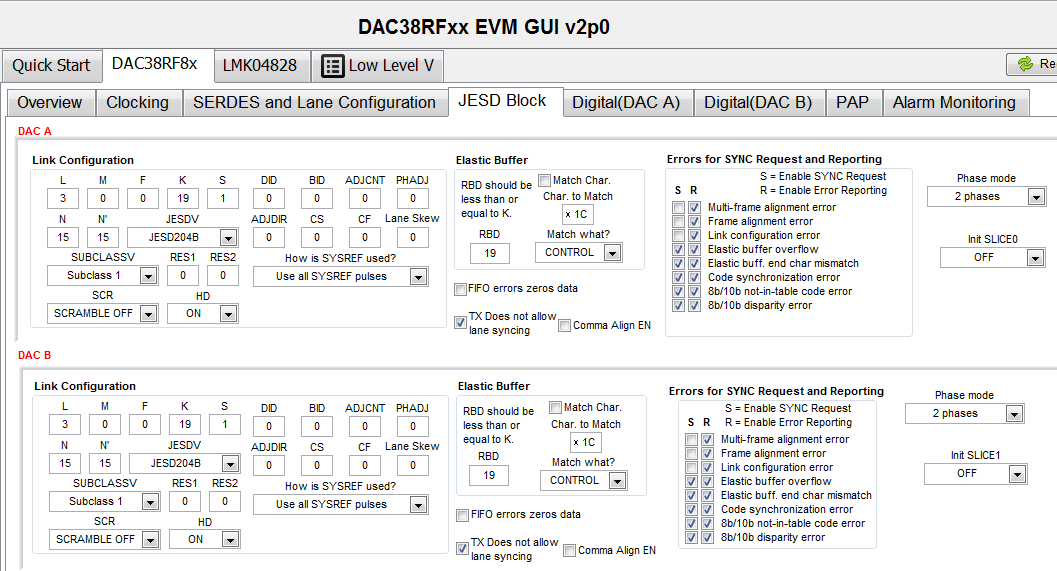

下面是 DAC38RF82EVM GUI 的 JESD 配置和 DAC 警报的屏幕截图。

Vivado 工程中 JESD204B IP 内核的链接参数如下所示。

有人能告诉我应该怎么做来调试这个项目吗?

非常感谢。

此致、

Tong