您好!

我们正在尝试从 FPGA 板生成 DAC 的 SPI 输入。

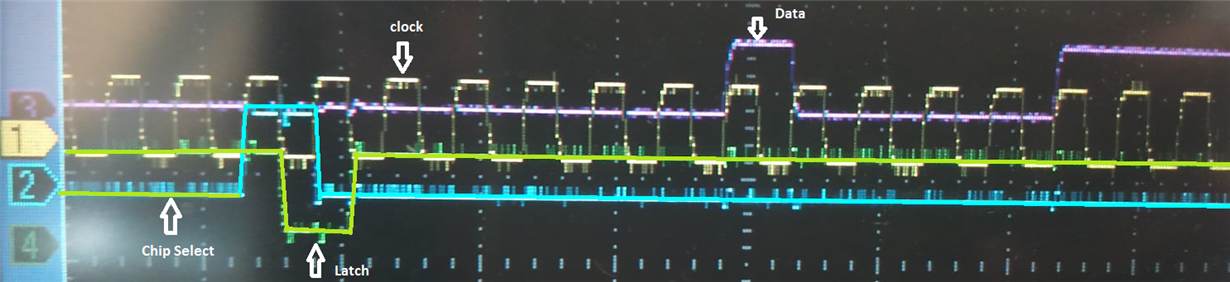

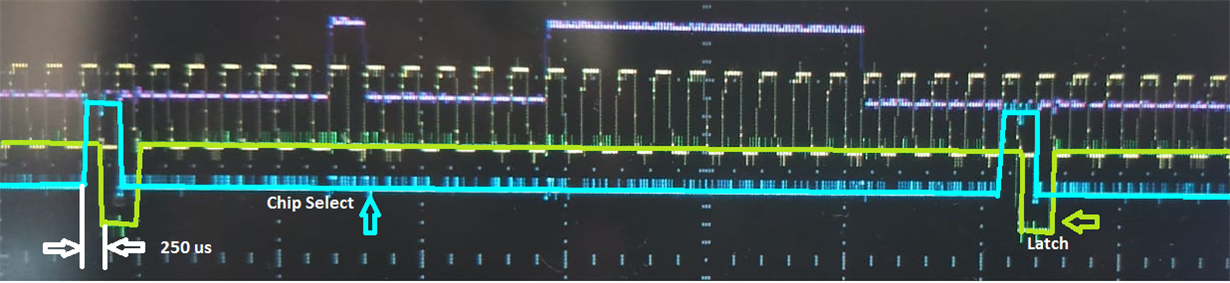

到目前为止、我们已根据时钟对波形进行了测试。 (SCLK)

SCLK 的频率为10MHz。 SPI 寄存器的地址为0100、我们要发送的数据为"111111111111"。

发送24位后、芯片选择在一个时钟周期内变为高电平、当芯片选择变为高电平时、锁存器变为低电平。

但我们无法看到 DAC 输出的任何输出。

还有其他需要注意的事项吗?

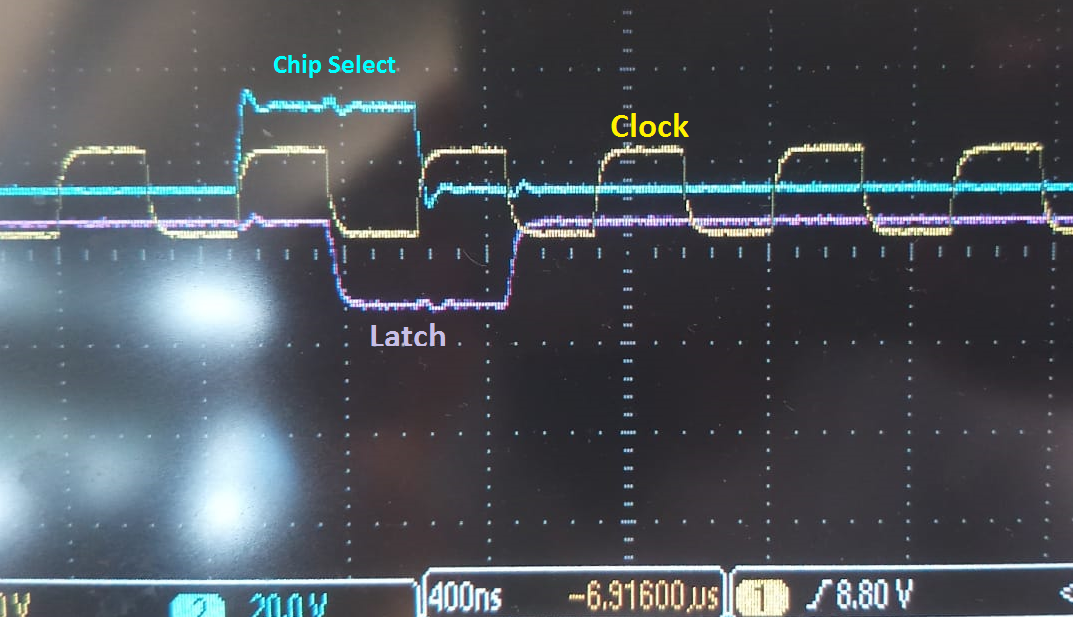

当我们在 MATLAB 中绘制进入 DAC 芯片的波形时、我们可以看到设置时间为负(即数据比时钟的上升沿晚一点)

此外、我如何确保输入中满足设置和保持时间要求。