Other Parts Discussed in Thread: ADC16DX370

您好!

已尝试验证 ADC16DX370 (在 FMC142上)和 KC705 FPGA JESD Rx 内核之间的 JESD 链路延迟是否固定。 我不关心确切的延迟值、我只想确认延迟在复位或 powercycle 时是否保持恒定。 理想情况下、JESD 子类1器件应具有确定性延迟。 用于测量此延迟的设置如下所示:

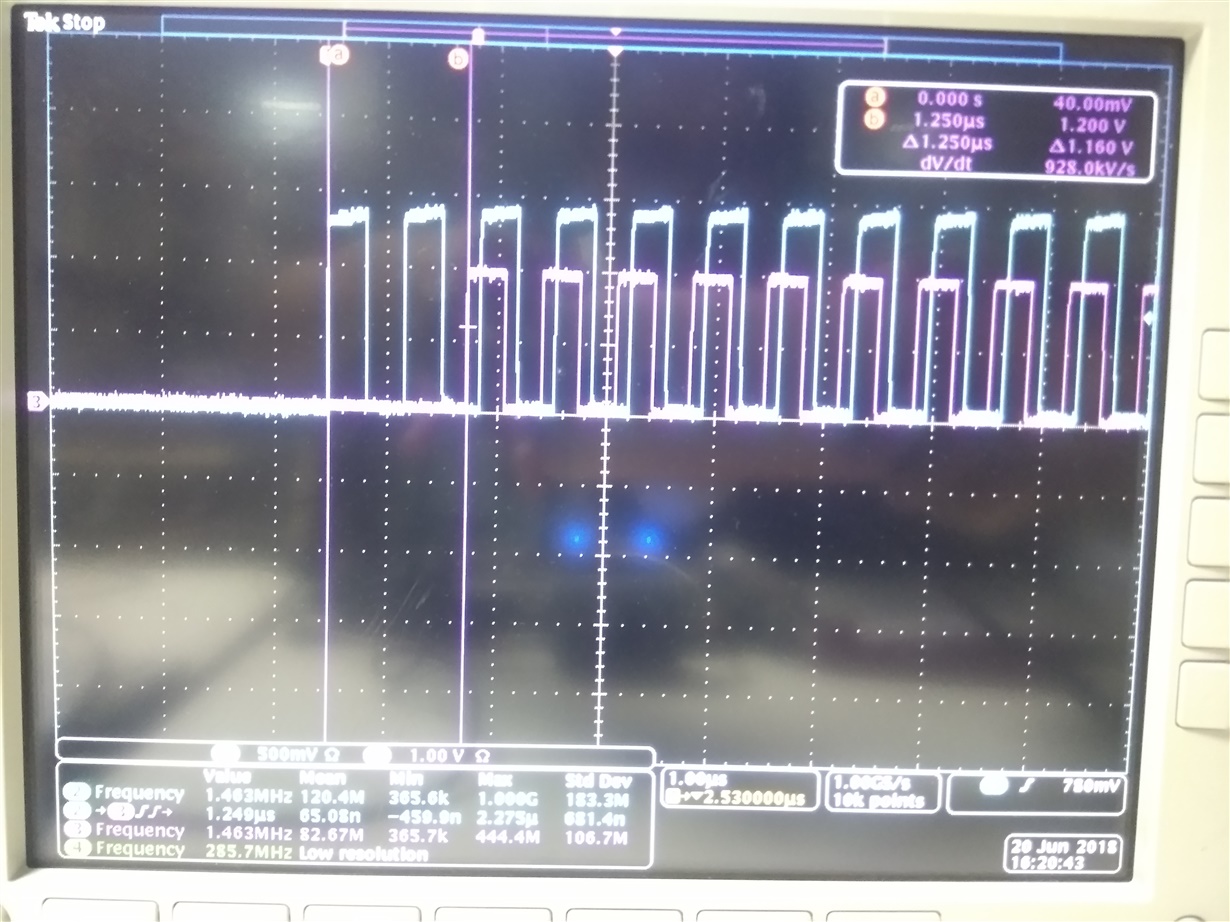

在 FPGA 中生成频率为1.4624999 MHz 的方波。 它输出到 SMA 端口、并通过分离器提供给示波器(通道2)和 FMC142 A0输入。

2.在 FPGA 中捕获 ADC 输出数据、其 MSB 位将输出到 SMA 端口并提供给示波器(通道3)

示波器中 CH2和 CH3信号之间的时序可提供延迟。 测量的延迟为1.249us

根据需要、该延迟在复位或下电上电时保持恒定。

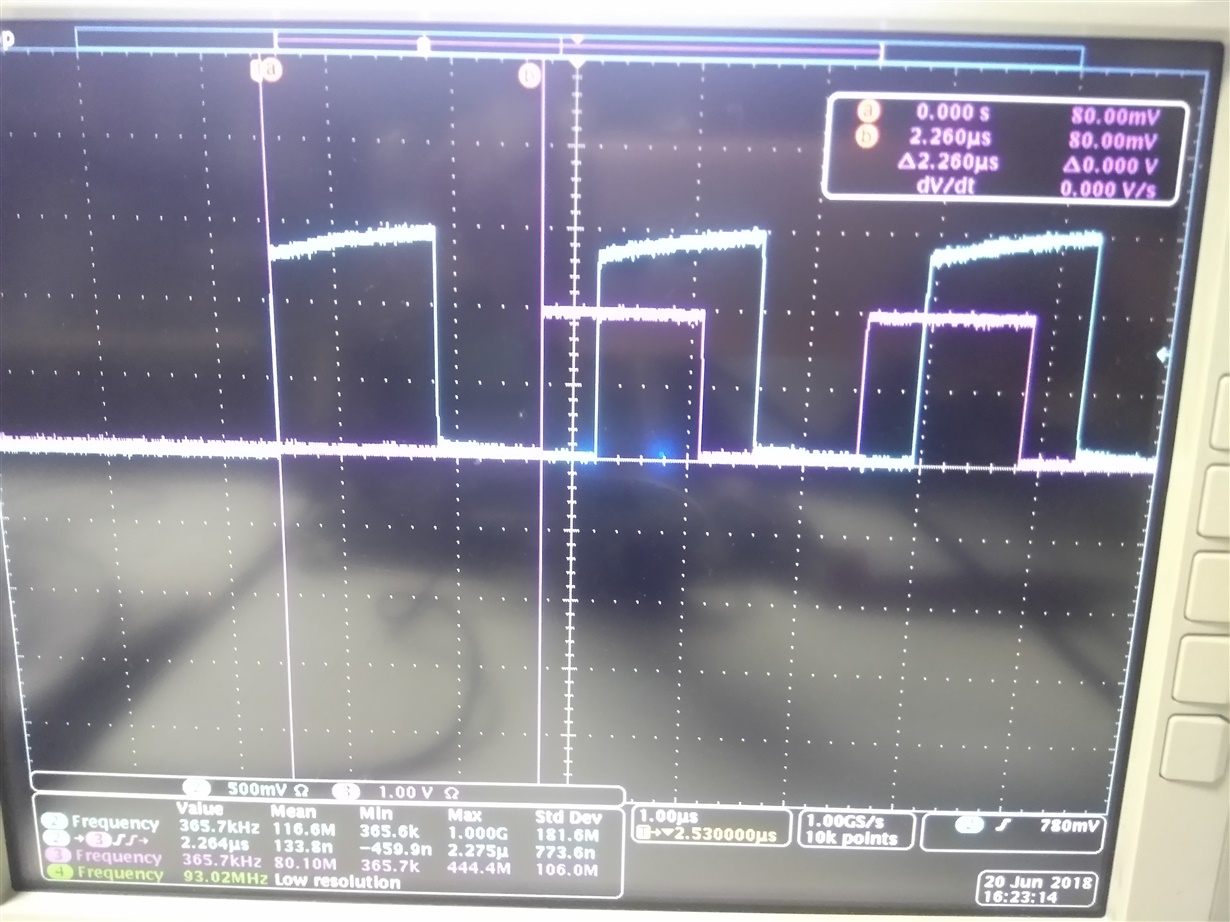

但是、当我将方波频率更改为0.365624999MHz 时、测得的延迟变为2.264us。

下面是两种情况下示波器测量的快照。

案例1 (第一个图像)案例2 (第二个图像)

蓝色波形是从 FPGA 生成的方波。

粉色波形是在 FPGA 中捕获的 ADC MSB 位。

为什么延迟随 ADC 输入频率变化? 无论 ADC 输入信号如何、都不应固定给定设置的延迟。

您能告诉我什么可能是问题吗?

谢谢、此致、

相扑