Other Parts Discussed in Thread: ADS54J64, TI-JESD204-IP

主题中讨论的其他器件: TI-JESD204-IP

您好!

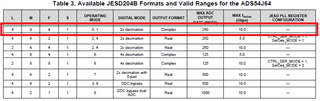

我的客户将使用具有以下 MODE1设置的 ADS54J64。

如果用户关闭未使用的转换器(例如通道 B、C、D)电源(客户设置中使用的通道 A 除外)、请告知是否没有问题。

谢谢你。

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: ADS54J64, TI-JESD204-IP

您好!

我的客户将使用具有以下 MODE1设置的 ADS54J64。

如果用户关闭未使用的转换器(例如通道 B、C、D)电源(客户设置中使用的通道 A 除外)、请告知是否没有问题。

谢谢你。

JH

您好、Jim、

感谢您的回复。

在上一个答案中、您说 FPGA 必须配置不同的 LMFS 设置、因为四个通道中的三个通道上没有数据。 如果是、是否应更改 ADS 的 LMFS 值、以便客户的设置正常工作?

如果在 Mode1设置中将只有 LMFS 更改为4211、是否会出现问题?

请告诉我们有关 LMFS 设置的更多信息、以便能够正常接收 CHA 数据。

此致、

JH

您好、Jim、

客户正在使用 TI-JESD204-IP 并对设置有疑问。

在 TI-JESD204-IP 中、即使在 K=32时也能正常工作。 是否有任何理由使用 K=16?

2.是否有建议的 SYSREF 速率? 如果您有 SYSREF 速率指南、请提供。

在 IP 中、ADC_Rx_SYNC_n 输出为低电平有效。 由于 ADS54J64 SYNCb 处于高电平有效状态、我可以在信号反转后发送它吗?

ADS54J64为14位分辨率。 将 IP 的 ADC_Resolution 设置为14和16之间是否存在差异?

5. cc_sysref_out_p/n 是否是可用于从 IP 生成和输出 sysref 的信号?

谢谢、

JH

您好、JH、

4.更改 ADC 分辨率会影响采样如何从通道数据中组合在一起。 对于 ADS54J64、应将 IP 的 ADC_RESULTION 设置为16、因为 ADS54J64 JESD204将每个样本发送16位、请参阅数据表的第7.5.3节。

5.cc_syref_ouptut 用于环回参考设计、可用于不提供 sysref 且不需要确定性延迟的设计。

此致、

David Chaparro

尊敬的 David:

感谢你的帮助。

客户对 TI JESD IP 还有其他问题。

1.是否可以查看以下 JESD_LINK_params.vh 以了解任何问题?

e2e.ti.com/.../jesd_5F00_link_5F00_params.zip

2. SYSREF 频率根据 N 值变化。是否有用作 SYSREF 的推荐频率范围?

3.当我关闭 ADS54J64的 CH B、C、D 并仅使用 CHA 时、我是否需要在 TI JESD204-IP 中设置一个通道?

我是否可以将其设置为4个通道并在内部忽略3个不必要的通道?

使用 Xilinx Zynq FPGA 时、Xilinx JESD IP 和 TI JESD204-IP 之间是否存在差异?

此致、

JH

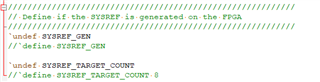

您好、JH、

1.我已经检查了 JESD_LINK_params.vh 文件并注意到三个需要更新的内容。 第一个是 ADC 分辨率。 对于 ADS54J64、应将 IP 的 ADC_RESULTION 设置为16、因为 ADS54J64 JESD204将每个样本发送16位、请参阅数据表的第7.5.3节。 第二个变化是将 RX_Lane_polarity 更新为4'b0000。 最后一项更改是取消定义 Sysref_Gen 信号、因为您将从 ADC EVM 提供 SYSREF。

使用较低的频率进行 SYSCREF 校准将更容易、因此选择1MHz 至5MHz 之间的频率应该可以正常工作。

3.在 IP 内部有一个通道启用参数 cfg_Rx_lane 使能、 可用于禁用未使用的通道。 您可以使用此选项禁用未使用的通道。 请注意、如果更新了此信息、则需要重新建立 JESD 链路。 这将允许头文件中的通道数仍然为4。

TI JESD204-IP 旨在帮助客户通过 TI 高速转换器快速实现正常的 JESD 链路。 TI IP 包含的功能使客户能够更轻松地使用我们的转换器和 IP 创建定制设计。

此致、

David Chaparro