主题中讨论的其他器件:ADS7066

您好!

我有关于 ADS7066的问题。

我连接了该 ADC 的评估板、当我希望最大采样率为250kSPS 时、SCLK 不能低于60MHz。

我需要将 SPI 接口与光隔离器隔离、因此 SCLK 信号的最大频率限制为25MHz。

我的问题是、为什么每个样本需要240个时钟周期?

我可以为应用使用较慢的 SCLK 吗?

在哪里可以看到250kSPS 下的最小 SCLK?

非常感谢、

Roee Kimchi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我有关于 ADS7066的问题。

我连接了该 ADC 的评估板、当我希望最大采样率为250kSPS 时、SCLK 不能低于60MHz。

我需要将 SPI 接口与光隔离器隔离、因此 SCLK 信号的最大频率限制为25MHz。

我的问题是、为什么每个样本需要240个时钟周期?

我可以为应用使用较慢的 SCLK 吗?

在哪里可以看到250kSPS 下的最小 SCLK?

非常感谢、

Roee Kimchi

Roee、

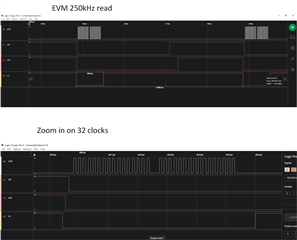

下面是时钟时序要求的说明。 EVM 使用32个时钟输出数据、但只需要24个时钟、因此可以以稍低的时钟速率运行。 但是、对于250kHz 的采样率、您将无法使用25MHz SCLK 信号。 导致要求更高时钟速率的主要因素是、您必须在转换周期内将 CS 保持为高电平。 最大转换周期指定为3200ns、因此您需要在该时间段内保持 CS 高电平。 这仅为数据计时留出800ns。 我要说、采样率的微小变化将在设置时钟频率方面提供相当大的灵活性。 例如、如果将采样率降低到200kHz、则可以使用1800ns 来计时数据(1/200kHz - 3200ns = 1800ns)。 假设为24.5个时钟、您可以使用13.6MHz 的时钟频率。 此外、这将使采集周期更长(1800ns)、从而使趋稳更容易(这有助于降低出现趋稳问题的可能性)。 下面是最小时钟速率计算的详细信息。 此外、我还展示了 EVM 使用更高时钟速率的原因(主要是因为 EVM 使用32个时钟、而不是最小24个时钟)。 我希望这对您有所帮助。

以下是基于24个数据时钟的时钟要求:

EVM 使用32个时钟进行数据传输。 以下是针对 EVM 软件的相同计算。

此致、

Art Kay