主题中讨论的其他器件:ADS4122、

您好!

我将使用 LVDS 时钟驱动器来驱动 ADS5296A 和 ADS4122的时钟输入。

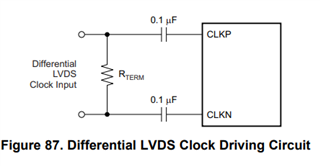

在 ADS5296A 的 DS 中、我发现以下内容:

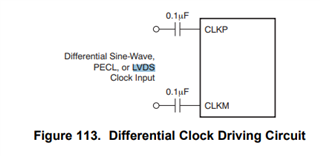

ADS4122同一问题的答案是:

请 建议在两种情况下将终端置于何处。

此致

Zeev Gerber

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Zeev、

感谢您与 TI 联系。

让我来解释一下上述电路为什么具有如图所示的端接。

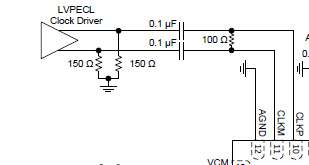

LVPECL 案例:

源极侧:为了获得足够的输出摆幅和驱动强度、需要使用电阻分压器对 LVPECL 引脚进行偏置。 该器件具有~82欧姆的上拉电阻(通常在器件内部)、预计会在引脚与 GND 之间放置一个外部电阻器 Rterm。 该电阻值通常介于120欧姆至240欧姆之间。

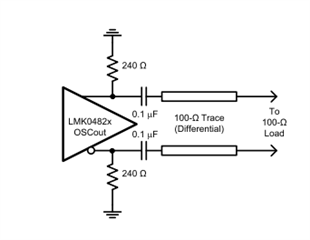

下图显示了典型的实现方案。 在耦合电容器之后、布线的特性阻抗为100欧姆、因此为了避免信号反射、需要放置一个100欧姆端接电阻、因此原理图看起来类似于您为 ADS4122共享的阻抗。

LVDS 情况:

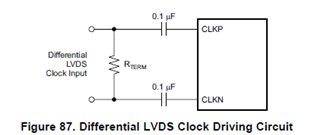

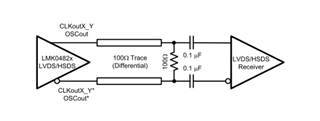

在 LVDS 时钟中、应该有一条从正到负端子的直流路径、并且特性阻抗为100欧姆。 因此、在耦合电容器之前、需要一个100欧姆的终端。

ADS5296A 和 ADS4122的数据表中也很明显:

因此、当使用 LVDS 时钟时、您可以将100欧姆端接放置在耦合电容器之前。

有关相同的更多信息、请参阅以下文档中的第10.4节"输出端接和偏置"

https://www.ti.com/lit/ds/symlink/lmk04828.pdf

谢谢、此致、

Abhishek