你好、

我想确认连接 ADS8686S SPI 协议的正确方法。

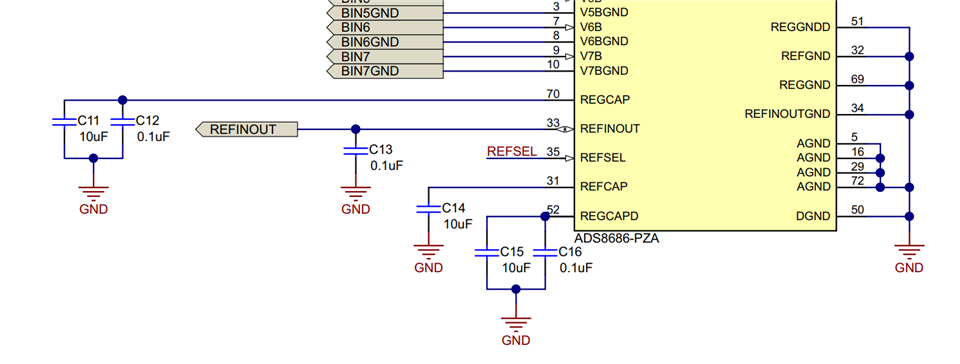

我从数据表和论坛中得到的结果与正确的数据计时和移位方法相冲突。 我 已将 Ser/Byte/PAR 引脚连接至高电平、并将 ByteSel 引脚连接至低电平。 我还在第一个 CONVST 上升沿之前发出至少1ms 的复位低电平和15ms 的延迟。

我的理解是、SCLK 应该空闲高电平、并且第一个下降沿应该在第一个 SDI 位上居中。 SCLK 的后续上升沿时钟输出 SDOA 和 SDOB 上的数据、此时 SDI 位的索引应更改。 我在下面附上了一个显示我的信号的时序图。 我最初时钟输出 SDI 上的所有零、然后为配置寄存器发出读取命令(0x0400)。 之后、我再次将 CS 拉低并继续为 SCLK 计时、但是、SDOA 线路 保持空闲状态。

这 是连接此芯片上 SPI 的正确方法吗? 还是应交换时钟边沿?

此致、

Shaun