tDACWAIT 是如何定义的? 数据表仅提供持续时间(2.4us)。 什么事件标志着 tDACWAIT 间隔的开始、在 tDACWAIT 之后、不能发生什么事件? 使用异步更新与同步更新时、这些点是否不同?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

tDACWAIT 是如何定义的? 数据表仅提供持续时间(2.4us)。 什么事件标志着 tDACWAIT 间隔的开始、在 tDACWAIT 之后、不能发生什么事件? 使用异步更新与同步更新时、这些点是否不同?

您好!

tdacwait 是事务之间的数字延迟、用于在器件内部释放总线。

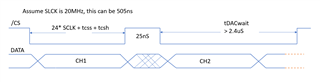

它定义为同步模式下后续 LDAC 下降沿之间的时间间隔或异步模式下后续 CS 上升沿之间的时间间隔。 基本上、tdacwait 必须被解释为下一个 DAC 命令的锁存边沿和 CS 下降边沿之间的延迟。

在 tdacwait 期间、数据寄存器更新被阻止。

例如、如果我们需要更新 Ch1数据、顺序应如下。 也适用于使用 LDAC 的多通道更新。

CH1 --> Tdacwait --> Ch1

希望这澄清了您的疑问。

此致、

AK

这是否意味着 tDACWAIT 在异步模式下不会对每个通道进行重叠? 我希望 tDACWAIT 按每通道应用、这样做是合法的:

通道 a -> tDACWAIT ->通道 A

通道 b -> tDACWAIT ->通道 B

通道 C -> tDACWAIT ->通道 C

通道 D -> tDACWAIT ->通道 D

该序列在小于4 x tDACWAIT 的周期内迭代。 例如、该序列应能够以192KHz (5.2us)迭代。 听起来就像您说的、tDACWAIT 适用于任何两个更新、甚至适用于不同的通道。

您好!

在异步模式下,由于不涉及/LDAC,我们可以将 tdacwait 定义为后续 CS 上升沿之间的间隔。 更新 Ch1时、可以通过拉低/CS 写入 Ch2、但帧长度应最小为2.4uS。 这是因为我们在各个渠道之间共享了资源。

因此、我要说的最佳方法如下所示。

因此、tdacwait 不是基于每个通道。 如果希望器件提供最佳吞吐量、请使用同步模式并写入所有寄存器、然后使用/LDAC 触发。