主题中讨论的其他器件: LMK04828

大家好、

(1) CLK2/CLK2C 是否接受 LVDS? 还是 LVPECL 仅可用?

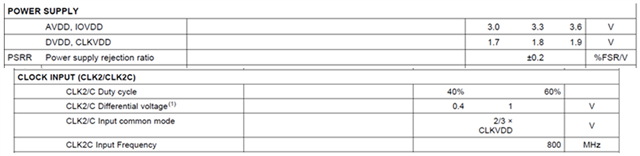

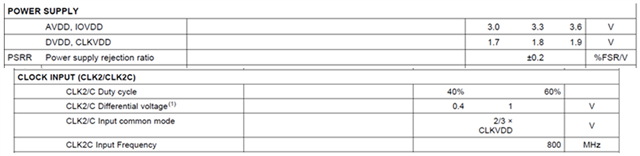

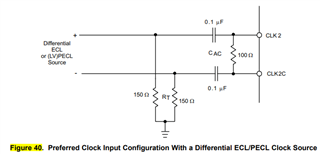

(2)对于 LVPECL、我想确认如何设置时钟接口。 根据数据表,它看起来是:

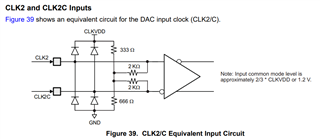

- VCM = CLKVDD 1.8V * 2/3 = 1.2V

- 1V 摆幅

-电源电压应该为3.3V 域

正确吗?

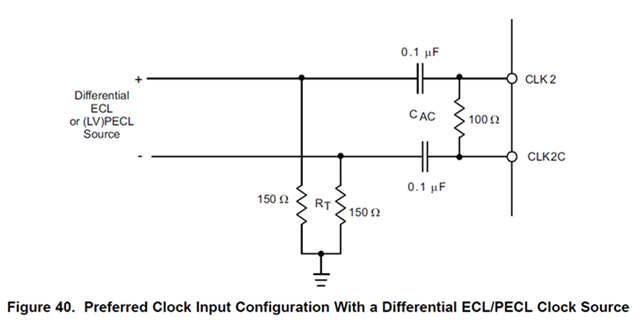

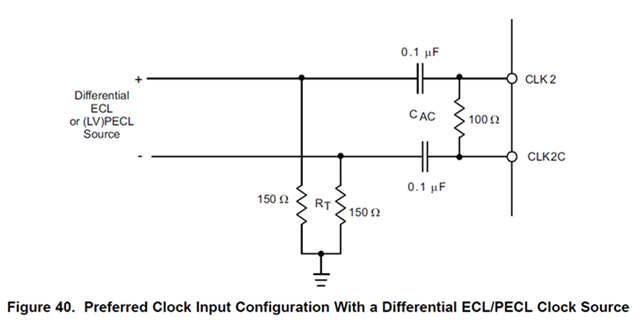

电路配置是否正确?

此致、

Ella

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

(1) CLK2/CLK2C 是否接受 LVDS? 还是 LVPECL 仅可用?

(2)对于 LVPECL、我想确认如何设置时钟接口。 根据数据表,它看起来是:

- VCM = CLKVDD 1.8V * 2/3 = 1.2V

- 1V 摆幅

-电源电压应该为3.3V 域

正确吗?

电路配置是否正确?

此致、

Ella

您好、Ella、

关于您的问题1.

[引用 userid="436821" URL"~/support/data-converters-group/data-converters/f/data-converters-forum/1194461/dac5688-clk2-clk2c-lvds-or-lvpecl ](1) CLK2/CLK2C 是否接受 LVDS? 或者 LVPECL 是否仅可用?[/QUERP]最好使用 LVPECL 或 HSDC 驱动器(在 LMK 系列上)以获得最佳的压摆率和最佳的抖动/相位噪声性能。 请与时钟团队讨论可为 DAC5688产生最佳相位噪声的时钟驱动器类型。

关于您的问题2.

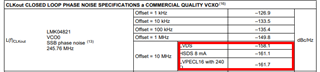

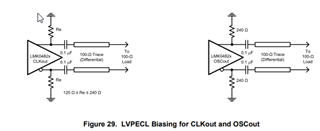

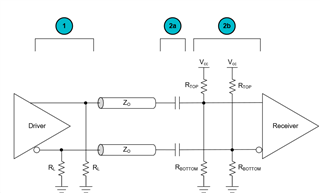

[引用 userid="436821" URL"~/support/data-converters-group/data-converters/f/data-converters-forum/1194461/dac5688-clk2-clk2c-lvds-or-lvpecl ](2)对于 LVPECL,我想确认如何设置时钟接口。 根据数据表,它看起来是: [/报价]不同的时钟驱动器和摆幅设置在 LVPECL 下拉电阻上具有不同的接口。 例如、LMK04828具有以下用于 LVPECL 终端的网络。

Ella、

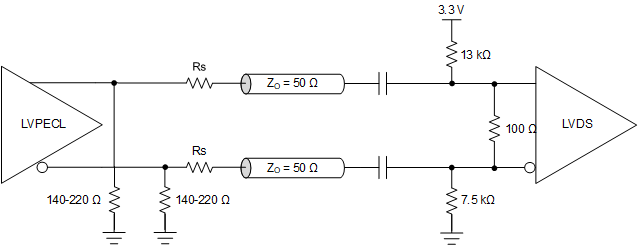

关于 LVPECL 至 LVDS 端接:

此致、

Jennifer

您好、Kang、Jennifer、

感谢你的答复。 我很困惑。 Kang 提到 CLK2/CLK2C 不接受 LVDS。 我们为什么需要 Jennifer 提到的 LVPECL 转 LVDS 终端?

[引用 userid="4249" URL"~/support/data-converters-group/data-converters/f/data-converters-forum/1194461/dac5688-clk2-clk2c-lvds-or-lvpecl/4502226 #4502226"]例如,LMK04828具有以下用于 LVPECL 终止的网络[/引用]

您共享的捕捉显示了驱动器端接。 接收器端接应该是什么样的?

我不熟悉此应用。 因此、我希望您对客户的善良和耐心的理解能够为客户提供正确的反馈。

此致、

Ella

您好、Kang、Jennifer、

谢谢。 让我再提一个问题!

1) 1)对于图40 (CLK2/C 的 LVPECL 输入)、我们如何设置共模电压1.2V? 对于 LVDS、我们需要如上所述为直流偏置放置电阻器网络。

2) 2)客户可以将 LVPECL 馈送到 CLK2/C 图40显示了 LVPECL 的配置、但我感到困惑。

- 150 Ω 至 GND 应该被放置在驱动器端 接收器( DAC5688的 CLK2/C)是否还需要该电流驱动电阻器?

- 100 Ω 终端用于 LVDS。 LVPECL 还需要该100 Ω 终端?

谢谢!

Ella

我可以再问一个问题吗?

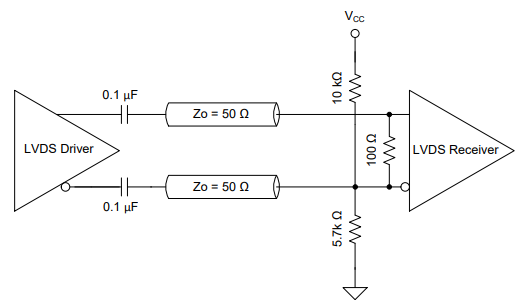

3) 3)我查看 了 LVDS 接口的 AN-1194故障安全偏置(修订版 C)(TI.com)。 DAC5688是否 为开路输入条件提供内部失效防护偏置? 客户希望了解 Jeniffer 先前展示的两种 LVDS 直流偏置配置之间的差异。 如果它具有内部失效防护偏置、则客户不一定会选择第一个选项。 对吧?

Ella

Ella、

我更仔细地查看了 DAC 数据表-有1.2V 内部偏置、这意味着不需要电阻器网络、您可以按原样遵循图40。

若要详细回答您过去的问题以供将来参考:

1) 1)对于图40 (CLK2/C 的 LVPECL 输入)、我们如何设置共模电压1.2V? 对于 LVDS、我们需要如上所述为直流偏置放置电阻器网络。

2) 2)客户可以将 LVPECL 馈送到 CLK2/C 图40显示了 LVPECL 的配置、但我感到困惑。

- 150 Ω 至 GND 应该被放置在驱动器端 接收器( DAC5688的 CLK2/C)是否还需要该电流驱动电阻器?

- 100 Ω 终端用于 LVDS。 LVPECL 还需要该100 Ω 终端?