Other Parts Discussed in Thread: LMK04832

主题中讨论的其他器件:LMK04832

大家好、

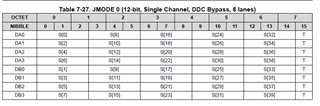

客户希望了解设计是否只能在单模式下使用每个 ADC 输出通道的前4位。 在数据表中、似乎无法回答让我们知道如何在单模式下连接输出的问题。

他们试图对现有设计进行逆向工程、但没有有关 ADC 设计的大量信息。 因此、他们正在寻找一个解释、为什么该设计仅在每个输出通道上使用前4位。

连接方式如下:

PD 被拉低。

CALTRIG、SDI、SCLK、SCS_N、SYNCSE_N、 SYSTREFP/N、NCOA0/1、NCOB0/1、SDO、ORA0/1、 ORB0/1都连接到 FPGA。

CLK_P/N 和 SYSREF_P/N 来自 LMK04832。

INA_P/N 连接到 RF 信号。

INB_P/N 未连接。

DA[0:3]、DB[0:3]连接到 FPGA

DA[4:7]、DB[4:7]未连接。

如果您需要更多信息、请告诉我。

谢谢、此致、

Marvin