Other Parts Discussed in Thread: DAC70508

主题中讨论的其他器件:DAC70508

大家好!

我在设置 DAC70508 DAC 的输出时遇到了一些问题。

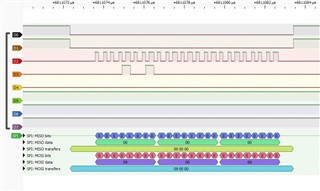

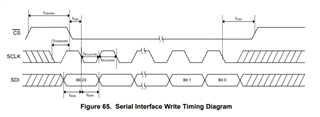

我认为我已经正确设置了 MSB、LSB 等的所有内容。。。 CS 线路和 SPI 在逻辑分析仪上看起来不错... 但 DAC 的输出没有变化。

我正在使用所有配置寄存器的标准设置、我只是不向 DAC 发送任何配置命令、除非发送测试命令尝试将 DAC1的输出设置为零... 但它只是保持相同的值。

我要发送

0x09 0x00 0x00

寄存器地址0x09是 DAC1、所有的零用来将输出设置为零... 但它不会改变...

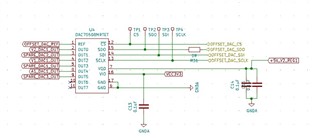

逻辑分析仪和下面的原理图。

在开始通信之前是否必须设置增益寄存器?

在默认设置下、当 CS 恢复为高电平时、DAC 是否应更新其输出?

我缺少什么?